No. 24-2304

# IN THE **United States Court of Appeals** FOR THE FEDERAL CIRCUIT

NETLIST, INC.,

Appellant,

v.

SAMSUNG ELECTRONICS CO., LTD., MICRON TECHNOLOGY INC., MICRON SEMICONDUCTOR PRODUCTS, INC., MICRON TECHNOLOGY TEXAS, LLC,

Appellees.

On Appeal from the U.S. Patent and Trademark Office, Patent Trial and Appeal Board, Nos. IPR2022-00615, IPR2023-00203

## **OPENING BRIEF FOR APPELLANT NETLIST, INC.**

Sara Margolis Catherine Martinez MOLOLAMKEN LLP 430 Park Avenue New York, NY 10022 (212) 607-8160

Elizabeth Kathleen Clarke Bonnie K. St. Charles MOLOLAMKEN LLP 300 N. LaSalle Street, Suite 5350 Chicago, IL 60654 (312) 450-6700 Jeffrey A. Lamken Rayiner Hashem Jennifer Elizabeth Fischell Lidiya Mishchenko Kayvon Ghayoumi MOLOLAMKEN LLP The Watergate, Suite 500 600 New Hampshire Avenue, N.W. Washington, D.C. 20037 (202) 556-2000 jlamken@mololamken.com

Counsel for Appellant Netlist, Inc.

## PATENT CLAIM AT ISSUE

### U.S. Patent No. 7,619,912, Claim 16

- [pre] A memory module connectable to a computer system, the memory module comprising:

- [a] a printed circuit board;

- [b] a plurality of double-data-rate (DDR) memory devices coupled to the printed circuit board, the plurality of DDR memory devices having a first number of DDR memory devices arranged in a first number of ranks;

- [c] a circuit coupled to the printed circuit board, the circuit comprising a logic element and a register, [c.i] the logic element receiving a set of input signals from the computer system, the set of input signals comprising at least one row/column address signal, bank address signals, and at least one chip-select signal, [c.ii] the set of input signals configured to control a second number of DDR memory devices arranged in a second number of ranks, the second number of DDR memory devices smaller than the first number of DDR memory devices and the second number of ranks less than the first number of ranks, [c.iii] the circuit generating a set of output signals in response to the set of input signals, the set of output signals configured to control the first number of DDR memory devices arranged in the first number of ranks, [c.iv] wherein the circuit further responds to a command signal and the set of input signals from the computer system by selecting one or two ranks of the first number of ranks and transmitting the command signal to at least one DDR memory device of the selected one or two ranks of the first number of ranks; and

- [d] a phase-lock loop device coupled to the printed circuit board, the phase-lock loop device operatively coupled to the plurality of DDR memory devices, the logic element, and the register,

- [e] wherein the command signal is transmitted to only one DDR memory device at a time.

FORM 9. Certificate of Interest

Form 9 (p. 1) March 2023

## UNITED STATES COURT OF APPEALS FOR THE FEDERAL CIRCUIT

#### **CERTIFICATE OF INTEREST**

**Case Number** 2024-2304

Short Case Caption Netlist, Inc. v. Samsung Electronics Co., Ltd.

Filing Party/Entity Netlist, Inc.

#### Instructions:

- 1. Complete each section of the form and select none or N/A if appropriate.

- 2. Please enter only one item per box; attach additional pages as needed, and check the box to indicate such pages are attached.

- 3. In answering Sections 2 and 3, be specific as to which represented entities the answers apply; lack of specificity may result in non-compliance.

- 4. Please do not duplicate entries within Section 5.

- 5. Counsel must file an amended Certificate of Interest within seven days after any information on this form changes. Fed. Cir. R. 47.4(c).

I certify the following information and any attached sheets are accurate and complete to the best of my knowledge.

Date: 02/18/2025

Signature: /s/ Jeffrey A. Lamken

Name: Jeffrey A. Lamken

FORM 9. Certificate of Interest

Form 9 (p. 2) March 2023

| <b>1. Represented</b><br><b>Entities.</b><br>Fed. Cir. R. 47.4(a)(1).                            | <b>2. Real Party in</b><br><b>Interest.</b><br>Fed. Cir. R. 47.4(a)(2).                                                                                 | <b>3. Parent Corporations</b><br><b>and Stockholders.</b><br>Fed. Cir. R. 47.4(a)(3).                                                                         |

|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Provide the full names of<br>all entities represented by<br>undersigned counsel in<br>this case. | Provide the full names of<br>all real parties in interest<br>for the entities. Do not list<br>the real parties if they are<br>the same as the entities. | Provide the full names of<br>all parent corporations for<br>the entities and all<br>publicly held companies<br>that own 10% or more<br>stock in the entities. |

|                                                                                                  | ☑ None/Not Applicable                                                                                                                                   | ☑ None/Not Applicable                                                                                                                                         |

| Netlist, Inc.                                                                                    |                                                                                                                                                         |                                                                                                                                                               |

|                                                                                                  |                                                                                                                                                         |                                                                                                                                                               |

|                                                                                                  |                                                                                                                                                         |                                                                                                                                                               |

|                                                                                                  |                                                                                                                                                         |                                                                                                                                                               |

|                                                                                                  |                                                                                                                                                         |                                                                                                                                                               |

|                                                                                                  |                                                                                                                                                         |                                                                                                                                                               |

|                                                                                                  |                                                                                                                                                         |                                                                                                                                                               |

|                                                                                                  |                                                                                                                                                         |                                                                                                                                                               |

|                                                                                                  |                                                                                                                                                         |                                                                                                                                                               |

|                                                                                                  |                                                                                                                                                         |                                                                                                                                                               |

|                                                                                                  |                                                                                                                                                         |                                                                                                                                                               |

|                                                                                                  | Additional pages attach                                                                                                                                 | ed                                                                                                                                                            |

FORM 9. Certificate of Interest

**4. Legal Representatives.** List all law firms, partners, and associates that (a) appeared for the entities in the originating court or agency or (b) are expected to appear in this court for the entities. Do not include those who have already entered an appearance in this court. Fed. Cir. R. 47.4(a)(4).

| ☑ None/Not Applicable | Additiona         | l pages attached  |

|-----------------------|-------------------|-------------------|

| Irell & Manella LLP   | Hong Annita Zhong | Jason G. Sheasby  |

| Jonathan M. Lindsay   | Phillip Warrick   | Michael W. Tezyan |

| Michael Fleming       |                   |                   |

**5. Related Cases.** Other than the originating case(s) for this case, are there related or prior cases that meet the criteria under Fed. Cir. R. 47.5(a)?

☑ Yes (file separate notice; see below) □ No □ N/A (amicus/movant)

If yes, concurrently file a separate Notice of Related Case Information that complies with Fed. Cir. R. 47.5(b). **Please do not duplicate information.** This separate Notice must only be filed with the first Certificate of Interest or, subsequently, if information changes during the pendency of the appeal. Fed. Cir. R. 47.5(b).

**6. Organizational Victims and Bankruptcy Cases**. Provide any information required under Fed. R. App. P. 26.1(b) (organizational victims in criminal cases) and 26.1(c) (bankruptcy case debtors and trustees). Fed. Cir. R. 47.4(a)(6).

$\square$  None/Not Applicable  $\square$  Additional pages attached

## TABLE OF CONTENTS

| INTR                    | ODUC                                                                                                  | CTION                 | 1                                                                                                         |  |

|-------------------------|-------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------|--|

| JURIS                   | SDICT                                                                                                 | IONA                  | L STATEMENT                                                                                               |  |

| ISSU                    | ES PR                                                                                                 | ESEN                  | ТЕD3                                                                                                      |  |

| STAT                    | TEME                                                                                                  | NT OF                 | THE CASE                                                                                                  |  |

| I.                      | Techr                                                                                                 | nological Background4 |                                                                                                           |  |

|                         | A.                                                                                                    | Memo                  | bry Modules and DRAM5                                                                                     |  |

|                         | B.                                                                                                    | Indus                 | try Standards and Cost Limit Memory-Module Capacity6                                                      |  |

| II.                     | Netlist Increases Memory Capacity by Enabling Standard Memory<br>Modules To Support Additional Ranks1 |                       |                                                                                                           |  |

|                         | A.                                                                                                    |                       | t Invents a Technique for "Rank Multiplication" and<br>ting Commands to a Single DRAM Chip10              |  |

|                         | B.                                                                                                    | The P                 | TO Awards Netlist the '912 Patent13                                                                       |  |

|                         | C.                                                                                                    |                       | 16 Survives Multiple Inter Partes Reexaminations and Is<br>ted to Its Current Form14                      |  |

| III. Procedural History |                                                                                                       | History17             |                                                                                                           |  |

|                         | A.                                                                                                    | Sams                  | ung's Petition                                                                                            |  |

|                         | B.                                                                                                    | The B                 | Board's Final Written Decision                                                                            |  |

|                         |                                                                                                       | 1.                    | Whether Skilled Artisans Would Understand Claim 16's<br>"Ranks" Necessarily Include Multiple DRAM Chips20 |  |

|                         |                                                                                                       | 2.                    | Priority from the '436 Patent and the '244 Provisional22                                                  |  |

| SUM                     | MARY                                                                                                  | OF A                  | RGUMENT                                                                                                   |  |

| STAN                    | JDARI                                                                                                 | D OF I                | REVIEW                                                                                                    |  |

| ARG  | UMEN  | VT                                                                                                                                                                                  | 30 |

|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| I.   |       | Board's Ruling That Claim 16 Covers a "Rank" Having Only<br>DRAM Device Requires Reversal                                                                                           | 33 |

|      | A.    | Claim 16 Covers Sending Commands to Only One DRAM<br>Among Multiple DRAMs in a Rank—Not Sending a Command<br>to <i>Every</i> DRAM in a "Rank" That Happens To Have Only One<br>DRAM | 35 |

|      | В.    | The Board's Contrary Construction Defies the Intrinsic<br>Evidence and Its Own Prior Decisions                                                                                      | 12 |

|      | C.    | The Board's Construction Cannot Be Sustained Regardless                                                                                                                             | 15 |

| II.  |       | Board's Determination That Ellsberry Teaches Claim 16 Is<br>oported Even Under the Board's Erroneous Construction                                                                   | 50 |

|      | А.    | Ellsberry's Figure 12 Does Not Show a Single-Device Rank                                                                                                                            | 50 |

|      | B.    | The Board's Conclusion Contradicts Its Own Prior Rulings                                                                                                                            | 54 |

| III. |       | Board's Determination That Ellsberry Is Prior Art Cannot Be                                                                                                                         | 55 |

|      | A.    | The Board Clearly Erred in Determining That Netlist's '436<br>Patent Lacks Written-Description Support for Claim 16                                                                 | 55 |

|      |       | 1. The Board's Determination That the '436 Patent Does<br>Not Disclose a "Register" Defies Law and Logic                                                                            | 55 |

|      |       | 2. The Board's Requirement of a Separate "Logic Element"<br>and "Register" Is Procedurally Improper and Incorrect                                                                   | 50 |

|      |       | 3. The Board's Ruling Defies Precedent and the APA                                                                                                                                  | 52 |

|      | B.    | Netlist Also Was Entitled to the Priority Date of the '244<br>Provisional Application                                                                                               | 53 |

|      | C.    | Vacatur Is Required for Additional Reasons                                                                                                                                          | 56 |

| CON  | CLUSI | ION                                                                                                                                                                                 | 56 |

## **TABLE OF AUTHORITIES**

## Page(s)

## CASES

| Alcon Rsch. Ltd. v. Barr Labs., Inc.,<br>745 F.3d 1180 (Fed. Cir. 2014)                        |

|------------------------------------------------------------------------------------------------|

| <i>In re Andersen</i> ,<br>743 F.2d 1578 (Fed. Cir. 1984)                                      |

| <i>Arendi S.A.R.L. v. Google LLC</i> ,<br>882 F.3d 1132 (Fed. Cir. 2018)2, 36                  |

| <i>Ariad Pharms., Inc. v. Eli Lilly &amp; Co.,</i><br>598 F.3d 1336 (Fed. Cir. 2010) (en banc) |

| <i>BASF Corp. v. Enthone, Inc.</i> ,<br>749 F. App'x 978 (Fed. Cir. 2018)43                    |

| <i>Biogen Idec, Inc. v. GlaxoSmithKline LLC,</i><br>713 F.3d 1090 (Fed. Cir. 2013)             |

| <i>Blackbird Tech LLC v. ELB Elecs., Inc.,</i><br>895 F.3d 1374 (Fed. Cir. 2018)42             |

| <i>Dell Inc. v. Acceleron, LLC,</i><br>818 F.3d 1293 (Fed. Cir. 2016)                          |

| <i>Elkay Mfg. Co. v. Ebco Mfg. Co.</i> ,<br>192 F.3d 973 (Fed. Cir. 1999)                      |

| <i>Exergen Corp. v. Wal-Mart Stores, Inc.</i> ,<br>575 F.3d 1312 (Fed. Cir. 2009)60            |

| <i>Falkner v. Inglis</i> ,<br>448 F.3d 1357 (Fed. Cir. 2006)                                   |

| <i>Fitbit, Inc. v. BodyMedia, Inc.,</i><br>IPR2016-00707, Paper 9 (PTAB Sept. 8, 2016)62       |

| <i>Google LLC v. EcoFactor, Inc.</i> ,<br>92 F.4th 1049 (Fed. Cir. 2024)                               |

|--------------------------------------------------------------------------------------------------------|

| Google LLC v. Netlist, Inc.,<br>810 F. App'x 902 (Fed. Cir. 2020)passim                                |

| Hologic, Inc. v. Smith & Nephew, Inc.,<br>884 F.3d 1357 (Fed. Cir. 2018)                               |

| Hybritech Inc. v Monoclonal Antibodies, Inc.<br>802 F.2d 1367 (Fed. Cir. 1986)                         |

| <i>Infinity Comput. Prods., Inc. v. Oki Data Am., Inc.,</i><br>987 F.3d 1053 (Fed. Cir. 2021)          |

| Innova/Pure Water, Inc. v. Safari Water Filtration Sys., Inc.,<br>381 F.3d 1111, 1116 (Fed. Cir. 2004) |

| <i>Intel Corp. v. Qualcomm Inc.</i> ,<br>21 F.4th 801 (Fed. Cir. 2021)                                 |

| Ironworks Pats. LLC v. Samsung Elecs. Co.,<br>798 F. App'x 621 (Fed. Cir. 2020)                        |

| <i>Jicarilla Apache Nation v. U.S. Dep't of Interior</i> ,<br>613 F.3d 1112 (D.C. Cir. 2010)           |

| <i>Kaken Pharm. Co. v. Iancu,</i><br>952 F.3d 1346 (Fed. Cir. 2020)41                                  |

| <i>Kraft Foods, Inc. v. Int'l Trading Co.,</i><br>203 F.3d 1362 (Fed. Cir. 2000)                       |

| LG Elecs., Inc. v. Bizcom Elecs., Inc.,<br>453 F.3d 1364 (Fed. Cir. 2006)                              |

| <i>Liebel-Flarsheim Co. v. Medrad, Inc.</i> ,<br>358 F.3d 898 (Fed. Cir. 2004)                         |

| <i>Linear Tech. Corp. v. ITC</i> , 566 F.3d 1049 (Fed. Cir. 2009)61                                    |

| Lockwood v. Am. Airlines, Inc.,<br>107 F.3d 1565 (Fed. Cir. 1997)                                              |

|----------------------------------------------------------------------------------------------------------------|

| <i>Lumi Legend Corp. v. Manehu Prod. All., Inc.,</i><br>PGR2024-00014, 2024 WL 3656822 (PTAB Aug. 5, 2024)62   |

| Lupin Ltd. v. Pozen, Inc.,<br>IPR2015-01775, Paper 15 (PTAB Mar. 1, 2016)25, 62                                |

| Lynk Labs, Inc. v. Samsung Elecs. Co.,<br>125 F.4th 1120 (Fed. Cir. 2025)                                      |

| <i>In re Magnum Oil Tools Int'l, Ltd.</i> ,<br>829 F.3d 1364 (Fed. Cir. 2016)60                                |

| Medtronic, Inc. v. Teleflex Innovations S.À.R.L.,<br>68 F.4th 1298 (Fed. Cir. 2023)                            |

| Medtronic, Inc. v. Teleflex Innovations, S.a.r.l.,<br>69 F.4th 1341 (Fed. Cir. 2023)                           |

| <i>Mission Integrated Techs., LLC v. Clemente,</i><br>No. IPR2023-01285, 2024 WL 752892 (PTAB Feb. 23, 2024)62 |

| <i>Motor Vehicle Mfrs. Ass'n of U.S., Inc. v. State Farm Mut. Auto. Ins. Co.,</i><br>463 U.S. 29 (1983)        |

| Nalpropion Pharms., Inc. v. Actavis Labs. FL, Inc.,<br>934 F.3d 1344 (Fed. Cir. 2019)                          |

| <i>Netword, LLC v. Centraal Corp.</i> ,<br>242 F.3d 1347 (Fed. Cir. 2001)44                                    |

| <i>Pers. Web Techs., LLC v. Apple, Inc.,</i><br>848 F.3d 987 (Fed. Cir. 2017)                                  |

| <i>Phillips v. AWH Corp.</i> ,<br>415 F.3d 1303 (Fed. Cir. 2005) (en banc)                                     |

| Powell v. Home Depot U.S.A., Inc.,<br>663 F.3d 1221 (Fed. Cir. 2011)61                                         |

| Power Integrations, Inc. v. Lee,<br>797 F.3d 1318 (Fed. Cir. 2015)                        | 65   |

|-------------------------------------------------------------------------------------------|------|

| <i>Rambus Inc. v. FTC</i> ,<br>522 F.3d 456 (D.C. Cir. 2008)                              | 26   |

| <i>In re Sang-Su Lee</i> ,<br>277 F.3d at 1338 (Fed. Cir. 2002)                           | , 65 |

| Southwall Techs., Inc. v. Cardinal IG Co.,<br>54 F.3d 1570 (Fed. Cir. 1995)               | 42   |

| <i>Starhome GmbH v. AT&amp;T Mobility LLC</i> ,<br>743 F.3d 849 (Fed. Cir. 2014)          | , 52 |

| <i>Tech. Props. Ltd. LLC v. Huawei Techs. Co.</i> ,<br>849 F.3d 1349 (Fed. Cir. 2017)     | 44   |

| <i>Thryv Inc. v. Click-to-Call Technologies LP</i> , 590 U.S. 45 (2020)                   | 66   |

| <i>TQ Delta, LLC v. CISCO Sys., Inc.,</i><br>942 F.3d 1352 (Fed. Cir. 2019)               | 54   |

| <i>V-Formation, Inc. v. Benetton Grp. SpA</i> ,<br>401 F.3d 1307 (Fed. Cir. 2005)         | 38   |

| Vas-Cath Inc. v. Mahurkar,<br>935 F.2d 1555 (Fed. Cir. 1991)                              | 59   |

| VirnetX Inc. v. Mangrove Partners Master Fund, Ltd.,<br>778 F. App'x 897 (Fed. Cir. 2019) |      |

| Virtek Vision Int'l ULC v. Assembly Guidance Sys., Inc.,<br>97 F.4th 882 (Fed. Cir. 2024) | 30   |

| <i>Vizio, Inc. v. Int'l Trade Comm'n,</i><br>605 F.3d 1330 (Fed. Cir. 2010)               | 38   |

| Wellman Inc. v. Eastman Chem. Co.,<br>642 F.3d 1355 (Fed. Cir. 2011)                      | , 65 |

## **STATUTES AND RULES**

| 5 U.S.C. §554(b)(3)      | 60         |

|--------------------------|------------|

| 5 U.S.C. §556(d)         | 60         |

| 28 U.S.C. §1295(a)(4)(A) | 2          |

| 35 U.S.C. §6             | 2          |

| 35 U.S.C. §141(c)        | 2          |

| 35 U.S.C. §311(b)        | 23, 29, 66 |

| 35 U.S.C. §318(a)        | 2          |

| 35 U.S.C. §319           | 2          |

## **OTHER AUTHORITIES**

| Micron Technology, Inc., <i>Technical Note: DDR4 Point-to-Point Design Guide</i> 1 (2020), |   |

|--------------------------------------------------------------------------------------------|---|

| https://www.mouser.com/pdfDocs/Micron_DDR4_Design_Guide.<br>pdf                            | 3 |

| Sequential Logic Circuits, https://www.electronics-tutorials.ws/<br>sequential/seq_1.html  | 9 |

| Webster's New International Dictionary (2d ed. 1934)                                       | 0 |

#### STATEMENT OF RELATED CASES

No appeal in or from this proceeding was previously before this or any other appellate court. The following cases may directly affect or be directly affected by this Court's decision in this case: *Netlist, Inc. v. Samsung Electronics Co., Ltd.*, No. 2:22-cv-00293 (E.D. Tex.); *Netlist, Inc. v. Micron Technology Texas, LLC*, No. 2:22-cv-00294 (E.D. Tex.); *Netlist, Inc. v. Google LLC*, No. 3:09-cv-05718 (N.D. Cal.). In addition, on January 21, 2025, this Court ordered that this appeal and the following appeals be treated as companion cases and assigned to the same merits panel: Nos. 25-1286 (lead), 25-1296 (member). ECF No. 22.

#### **INTRODUCTION**

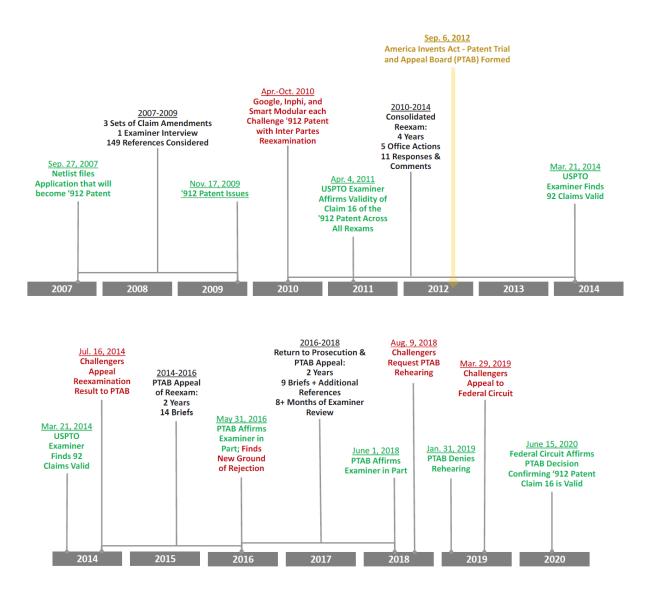

Claim 16 of Netlist's '912 patent has been subjected to three exhaustive inter partes reexaminations: one sought by Google, another by Smart Modular, and a third by Inphi. It survived sprawling PTO proceedings spanning 10 years that involved myriad unpatentability grounds; five office actions; more than twenty briefs; two appeals to the PTAB; and an appeal to this Court. It survived because the Examiner and the Board adopted—and Netlist accepted—a construction of a key term to require that claimed "ranks" contain *two or more* memory devices. That construction reflected industry standards, which required ranks to contain multiple devices.

But when this IPR petition was filed by Google's supplier, Samsung, the Board reversed course below and found the claim unpatentable. It did not identify new art. It changed its construction so the claimed ranks can contain only *a single* memory device—a construction *diametrically opposed* to the construction the Board applied in the reexamination. That about-face is troubling as a matter of agency consistency. But it is also improper as a matter of patent law. The consensus in the reexamination about the meaning of "rank" in claim 16—among the Examiner, Netlist, and the Board there—is powerful prosecution-history intrinsic evidence skilled artisans would rely on to understand that term. The Board in this IPR never suggested otherwise. And the Board was required to "exclude any interpretation that was disclaimed during prosecution." *Arendi S.A.R.L. v. Google LLC*, 882 F.3d 1132,

1135 (Fed. Cir. 2018). But the Board did the opposite—departing from the claim's text, the specification, and industry standards in the process.

Worse, the sole reference on which the Board relied—Ellsberry—does not teach claim 16's subject matter even under the Board's new construction. And Ellsberry was not even prior art to claim 16. The '912 patent claims priority to *two* filings—Netlist's '436 patent and '244 provisional—that antedate Ellsberry. The Board declared that neither filing provides written-description support for claim 16. But the "register" the '436 patent supposedly does not disclose was conventional already—and the '436 patent disclosed it by reciting "sequential logic," which undisputedly requires "a register" or its "equivalent." The Board's analysis of the '244 provisional is even more flawed. Post-grant review procedures serve an important purpose in our patent system. But they were not designed as vehicles for relitigating issues until a different PTAB panel reaches a different result.

#### JURISDICTIONAL STATEMENT

The Board had jurisdiction under 35 U.S.C. §§6, 318(a). It issued a final written decision on April 17, 2024. Appx1-56. Director review was denied on July 10, 2024. Appx57-59. Netlist appealed on September 10, 2024. Appx109. This Court has jurisdiction under 28 U.S.C. § 1295(a)(4)(A) and 35 U.S.C. §§141(c), 319.

#### **ISSUES PRESENTED**

In this IPR, the Board ruled that claim 16 is obvious in light of the Ellsberry reference. The Board previously upheld the same claim in three earlier inter partes reexaminations, and this Court affirmed. The issues presented are:

1. Whether the Board's construction of claim 16 was erroneous, where it contradicts the construction the Board adopted in finding the same claim patentable during prior reexaminations.

2. Whether the Board's obviousness determination was unsupported by substantial evidence.

3. Whether the Board's determination that Ellsberry is prior art is erroneous, where the '912 patent claims priority to two filings that antedate Ellsberry and provide written-description support for claim 16.

### **STATEMENT OF THE CASE**

This appeal concerns Netlist's patented technology for increasing the capacity and speed of memory modules while reducing power usage. For its inventions, Netlist received U.S. Patent No. 7,619,912 ("the '912 patent") in 2009. The patent then spent a decade in reexamination proceedings in which the Examiner and the Board repeatedly affirmed claim 16's patentability. This Court affirmed. *Google LLC v. Netlist, Inc.*, 810 F. App'x 902 (Fed. Cir. 2020). In this IPR, however, the Board invalidated claim 16 over Ellsberry—a reference considered during initial examination—by adopting a claim construction diametrically opposed to the one it adopted during reexamination.

### I. TECHNOLOGICAL BACKGROUND

Computers need increasingly more memory to support sophisticated applications such as artificial intelligence. Appx19694. Increasing the number of memory modules—circuit boards with memory chips—quickly ceased to be an option. Appx11604. Computers have a limited number of slots into which memory modules may be installed. Appx96(32:29-31). To increase the memory that could be installed into each computer, manufacturers needed to increase the capacity of each memory module. Appx96(32:29-31).

Restrictions imposed by industry standards, and the cost of higher-capacity memory devices, significantly limited manufacturers' ability to do so. Appx11664; Appx81(2:39-41). But Netlist's '912 patent provided a new approach—"rank multiplication" with individually addressable memory devices—for expanding the capacity of standards-conforming memory modules while reducing cost, increasing speed, and reducing power usage. Appx81(2:16-23, 2:39-40); Appx86(12:39-43); Appx83(5:1-5).

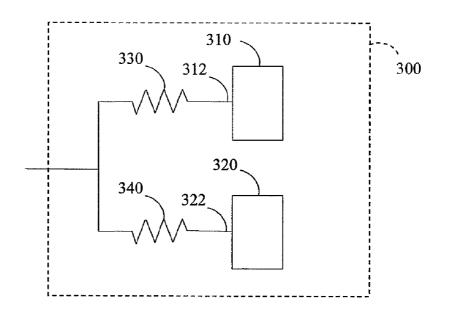

## A. Memory Modules and DRAM

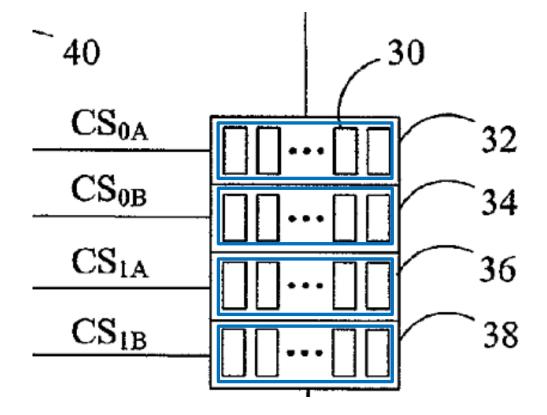

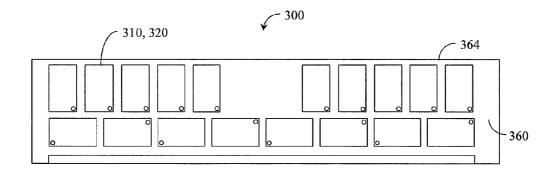

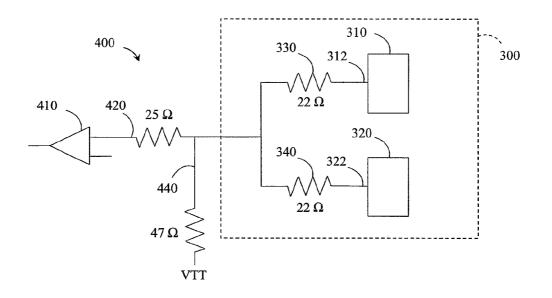

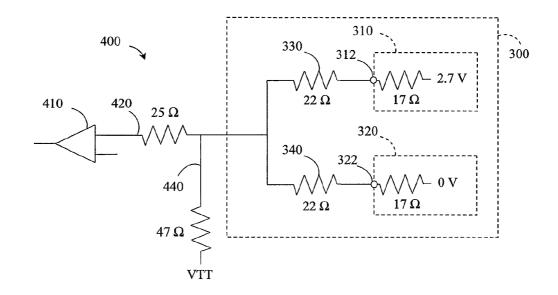

Memory modules store data in dynamic random-access memory ("DRAM") chips. Appx81(1:25-36). A memory module includes a circuit board (green) with individual DRAM chips (black rectangles) attached. Appx81(1:25-27).

Appx20251. The gold edge connector on the bottom of the module plugs into a slot on the computer's motherboard, making the memory on the module available to the computer. Appx83(6:4-11); Appx20250.

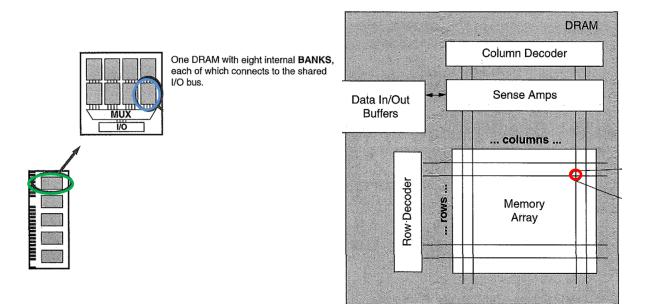

As shown below, on the left, a DRAM chip (green) includes a plurality of memory "banks" (blue). Appx11608. As shown on the right, each memory bank includes "memory array[s]" consisting of a grid of storage cells (*e.g.*, red circle) arranged in "rows" and "columns." Appx11606; Appx11608.

Appx11608; Appx11606 (annotated). When the CPU's "memory controller" stores data to (writes) or retrieves data from (reads) a storage cell, it locates the desired cell by specifying its "address" in terms of a "bank address," "row address," and "column address." Appx11606-08; Appx11699.

### **B.** Industry Standards and Cost Limit Memory-Module Capacity

The capacity of a memory module—the amount of data it can store—depends on the capacity of each DRAM chip and the number of DRAM chips on the module. Appx81(2:24-25). Capacity can be increased by either increasing the *capacity of each DRAM chip*, or increasing the *number* of DRAM chips.

Cost posed a barrier to increasing individual chip capacity. Higher-capacity DRAM chips are generally more expensive per unit of capacity than lower-capacity chips. Appx83(5:1-5). For example, two 256-Mb DRAM devices together may cost less than one 512-Mb device, even though two 256-Mb devices together have 512

Mb of capacity. Appx82-83 (4:47-5:5). To increase capacity using available, costeffective DRAM chips, memory-module makers sought ways to increase the number of DRAM chips on each memory module. Appx83 (5:1-5).

Industry standards, however, were a barrier to increasing the number of DRAM chips on each module. To ensure interoperability, the industry group JEDEC sets standards for DRAM memory modules. Appx11709. The "vast majority" of DRAM memory modules follow "JEDEC specifications." Appx18284(¶19). The relevant JEDEC standard—"DDR" ("Double Data Rate")—limits the number of memory chips on each module in two ways. Appx20259-344.

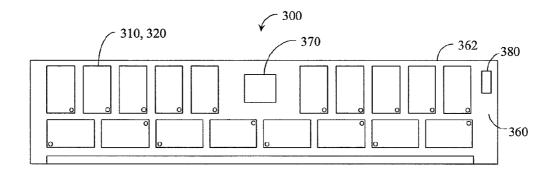

*First*, the CPU's memory controller reads/writes a set number of bits at a time in parallel. Appx11809. The *memory module* must read/write that number of bits—known as the module's "bit width"—simultaneously. Appx11809. Relevant JEDEC "DDR" standards specify modules of "64" or "72" bits. Appx12184; Appx11699 & n.1; Appx18460(¶255). Memory modules that did not comply with those standard bit widths would not function correctly. Appx11699-700.

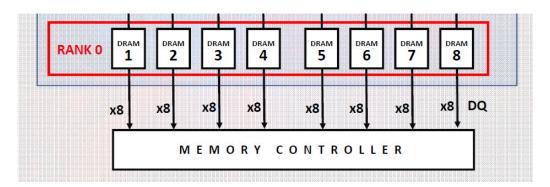

Individual *DRAM chips* also must read/write a set number of bits in parallel— 4, 8, or 16 bits at a time under the JEDEC DDR standard. Appx86(12:39-55); Appx11267-70. Thus, multiple DRAM chips must work in concert to produce the 64- or 72-bit width the DDR standard requires. Appx11703. To achieve that, DRAM chips on each memory module are organized into "ranks," where each rank

7

consists of multiple chips operating together to read/write the required number of bits at a time. Appx11703-04; Appx20253; *see* Appx19644. For example, to form a 64-bit-wide memory module, DRAM chips may be organized into ranks of 8 chips each, where each chip is 8 bits wide ( $8 \times 8 = 64$ ). Appx18455.

Appx20253 (cropped). Alternatively, the chips may be organized into ranks of 16 memory chips, where each chip is 4 bits wide ( $16 \times 4 = 64$ ). Appx18455.

As Petitioner Micron recognized, "[t]he term rank was created by JEDEC" to describe an arrangement of memory chips adding up to the "64 or 72 bits" required for the "module." Appx19644. The term "rank"—referring to a "line of soldiers ranged side by side," *Webster's New International Dictionary* 2061 (2d ed. 1934)— aptly described DRAM chips arranged side-by-side to provide the memory module's bit width, as shown above. Appx19644.

*Second*, the JEDEC DDR standards limited the number of ranks in each memory module. Appx81(2:39-40). Under the standard, the memory controller provided one or more "chip-select" signals that are used to distinguish between ranks in each memory module. Appx81(2:34-41). The number of chip-select signals

available under the standard typically limited each memory module to at most two ranks. Appx81(2:34-41).

Those requirements—memory-module bit-width and a maximum of two rank-select signals—limited the number of DRAM chips on, and thus the total capacity of, each module. The number of chips per rank was dictated by the required bit width of the memory module; and the number of ranks per memory module was limited by the number of chip-select signals. Appx11699 & n.1 (bit width); Appx84(7:23-27) (chip-select). For example, memory modules could be 64-bits wide and support up to two ranks. Appx11699 & n.1; Appx84(7:23-27). If available DRAM chips were 8 bits wide, each rank would have 8 chips (8 × 8 = 64), and each module would have 16 chips (2 ranks of 8 chips each). Appx18455.

Appx20253.

## II. NETLIST INCREASES MEMORY CAPACITY BY ENABLING STANDARD MEMORY MODULES TO SUPPORT ADDITIONAL RANKS

A pioneer in memory technology, Netlist has developed, manufactured, and supplied cutting-edge memory products to companies including IBM, Dell, HP, and Apple.

Netlist devised a way to cost-effectively increase memory-module capacity by increasing the number of ranks—while maintaining compatibility with JEDEC standards. Netlist's improved memory modules increased server memory capacity using more, cheaper, lower-capacity DRAM chips (instead of costly higher-capacity chips). That increased performance without requiring changes to existing memory controllers or motherboards. Netlist also invented a way for memory controllers to send commands to *individual* DRAM devices in a rank—in contrast to the prior art that broadcasted commands to *all* devices in the rank. That enabled sending individually tailored power-management and calibration commands to each DRAM chip to optimize that chip's performance and power usage.

## A. Netlist Invents a Technique for "Rank Multiplication" and Targeting Commands to a Single DRAM Chip

Netlist's patented invention overcame the barrier to greater numbers of ranks that industry standards had imposed. It allowed the memory module to have more ranks of lower-capacity chips (*e.g.*, four ranks of lower-capacity chips) while *appearing* to the CPU to have the smaller number of ranks of higher-capacity chips the JEDEC DDR standard required (*e.g.*, two ranks of higher-capacity chips). Appx84(7:5-19); Appx96(32:27-49).

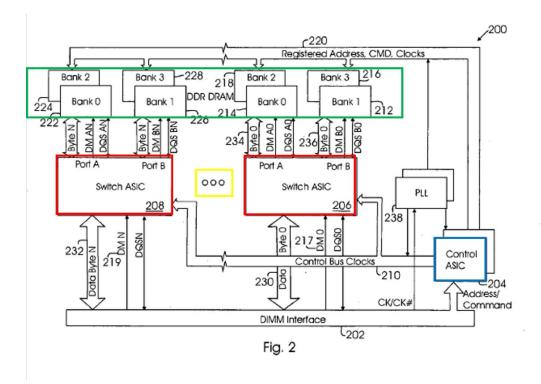

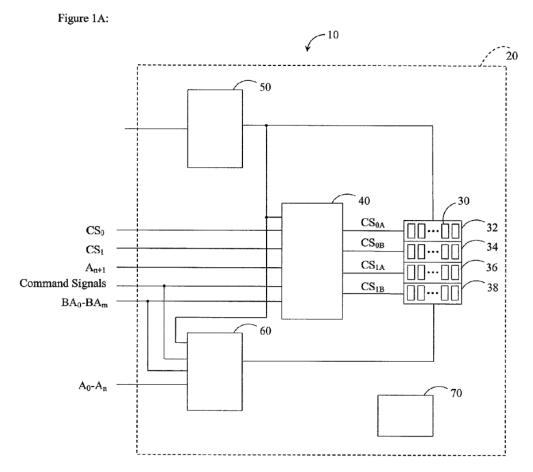

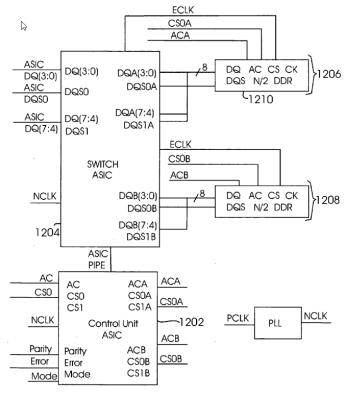

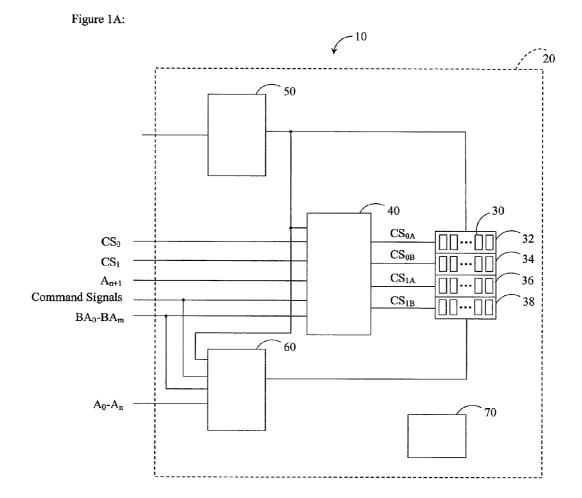

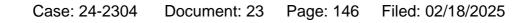

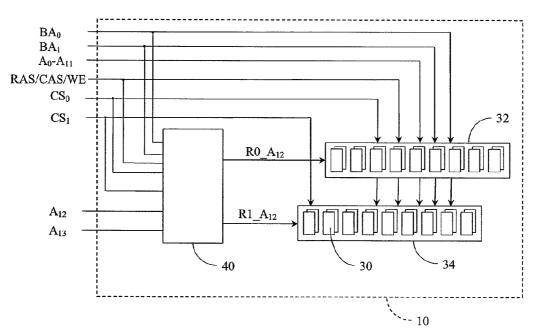

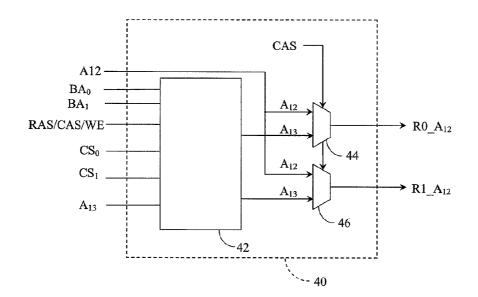

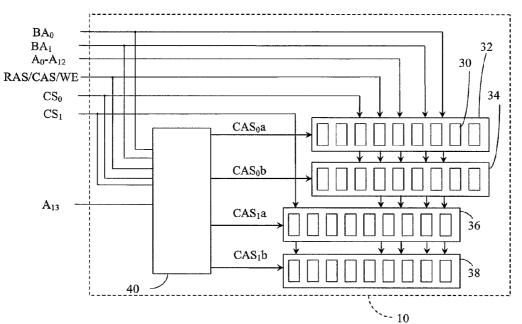

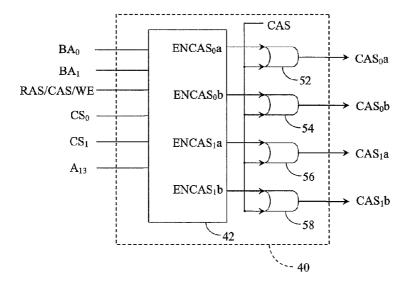

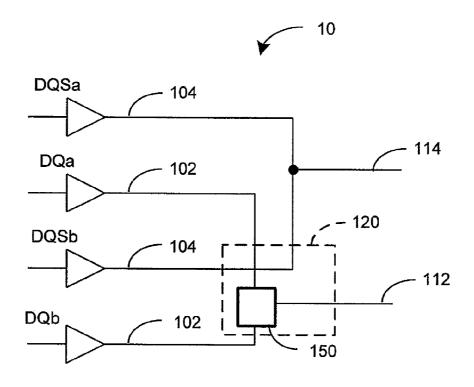

1. To achieve that result, Netlist engineers placed a logic circuit inside the memory module. That circuit intercepts chip-select and address signals intended to control the smaller number of ranks; it then creates additional signals to control the larger number of ranks actually present in the module. Appx83-84(6:55-7:6); Appx63(Fig. 1A). Memory-controller signals designed to control just two ranks of memory devices, for example, can be utilized to control four ranks.

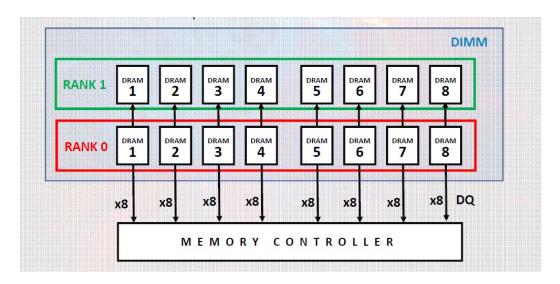

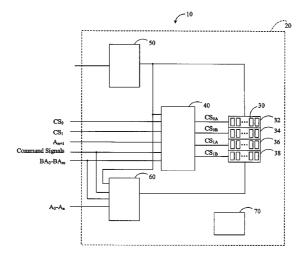

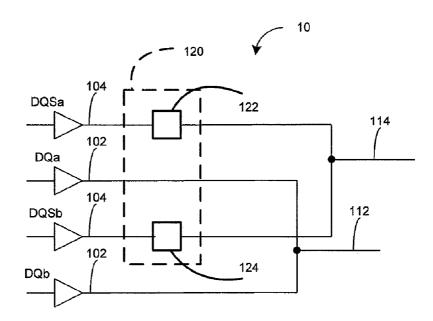

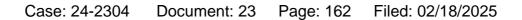

Figure 1A of the '912 patent illustrates an embodiment of the invention:

Appx63 (Fig. 1A) (annotated). A memory module (10) has DRAM chips arranged in four ranks (32, 34, 36, and 38, purple). Appx83 (5:22-25; 6:31-35). The CPU's "memory controller" sends a set of control and address signals, including *two* chipselect signals (CS<sub>0</sub> and CS<sub>1</sub> in green box) to control *two* ranks. Appx84(7:35-53); Appx86 (11:43-48). A "logic element" (40, red) receives those signals and generates *four* chip-select signals (CS<sub>0A</sub>, CS<sub>0B</sub>, CS<sub>1A</sub>, CS<sub>1B</sub> in blue box) for the *four* ranks located on the memory module. Appx86 (11:62-67). Meanwhile, a "register" (60, orange) receives and buffers address signals and sends them to "the appropriate ranks of memory devices." Appx84 (7:43-53). The logic element and register can be "separate components" or "portions of a single component." Appx83 (5:37-42).

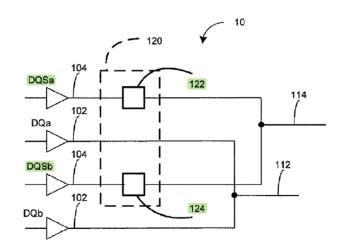

2. Netlist also invented "per-DRAM addressability" ("PDA"). Conventionally, memory controllers broadcast commands—such as for configuring DRAM chips—simultaneously to *all* DRAM chips in a rank, which "operate[d] in lockstep." Appx11702. PDA enabled memory controllers to isolate "only one" DRAM chip in the rank at a time—out of the several in the rank—and send commands to that chip alone. Appx84(8:50-54); Appx105(7:20-24); *see* Appx18298-301(¶¶40-43).

Per-DRAM addressability provided significant benefits. Appx19343. It saved power by allowing the memory controller to put "a single DRAM device" in a rank into a "maximum power-saving" mode. Appx19333. PDA also enabled memory controllers to tune key configuration parameters to individual DRAM

12

devices, maximizing each chip's speed and power usage. Micron Technology, Inc., *Technical Note: DDR4 Point-to-Point Design Guide* 1, 12-14 (2020), https://www.mouser.com/pdfDocs/Micron\_DDR4\_Design\_Guide.pdf. PDA now is part of JEDEC's specifications. Appx16531-33; Appx19287.

## B. The PTO Awards Netlist the '912 Patent

Netlist's '912 patent covers its rank-multiplication and per-DRAM addressa-

bility innovations.

Claim 16 is reproduced below:

- [pre] A memory module connectable to a computer system, the memory module comprising:

- [a] a printed circuit board;

- [b] a plurality of double-data-rate (DDR) memory devices coupled to the printed circuit board, the plurality of DDR memory devices having a first number of DDR memory devices arranged in a first number of ranks;

- [c] a circuit coupled to the printed circuit board, the circuit comprising a logic element and a register,

- [c.i] *the logic element receiving a set of input signals from the computer system*, the set of input signals comprising at least one row/column address signal, bank address signals, and at least one chip-select signal,

- [c.ii] the set of input signals configured to control a second number of DDR memory devices arranged in a second number of ranks, the second number of DDR memory devices smaller than the first number of DDR memory devices and the second number of ranks less than the first number of ranks,

- [c.iii] *the circuit generating a set of output signals in response to the set of input signals*, the set of output signals configured to control the first number of DDR memory devices arranged in the first number of ranks,

- [c.iv] wherein the circuit further responds to a command signal and the set of input signals from the computer system by selecting one or two ranks of the first number of ranks and *transmitting the command signal to at least one DDR memory device of the selected one or two ranks of the first number of ranks*; and

- [d] a phase-lock loop device coupled to the printed circuit board, the phase-lock loop device operatively coupled to the plurality of DDR memory devices, the logic element, and the register,

- [e] wherein the command signal is transmitted *to only one DDR memory device at a time*.

Appx103(3:9-43) (emphasis added). Limitation 1[c.i]-[c.iii] reflects rank multipli-

cation, while limitations 1[c.iv] & 1[e] reflect per-DRAM addressability.

## C. Claim 16 Survives Multiple Inter Partes Reexaminations and Is Restated to Its Current Form

Claim 16 has an extensive prosecution history. Originally, the preamble and limitations [a]-[d] were recited in independent claim 15. Appx10650-51. Claim 16 originally depended from claim 15 and further recited what is now claim 16's limitation [e]: "wherein the command signal is transmitted to only one DDR memory device at a time." Appx10651.

Shortly after the '912 patent issued, Google, Smart Modular Technologies, and Inphi each sought reexamination of the patent, including claims 15 and 16.

Appx10487. The reexamination ultimately consumed over ten years, including two appeals to the Board and an appeal to this Court:

1. In the first round of reexamination, the Examiner found claim 15 unpatentable, but upheld claim 16. The Examiner rejected the argument that claim 16 was obvious in view of Amidi. "The claims," the Examiner explained, "require transmission of a command signal to only one DDR memory device at a time"—*i.e.*, "only one DDR memory device at a time *when there is a plurality of memory devices in a rank*." Appx6375 (emphasis added). The claim thus was not disclosed by prior art where, as in Amidi, a command is "transmitted to *all devices*" in a rank simultaneously. Appx6413 (emphasis added). Based on the Examiner's determination, Netlist amended the claims to restate claim 16 as an independent claim and cancel claim 15. New claim 16 incorporated the limitations of original independent claim 15 along with the limitations of original dependent claim 16 (with no other changes). Appx5615-16; Appx5652.

One requester argued that Amidi taught sending a signal to only one memory device at a time by teaching a "rank" that purportedly "encompasses" just "*one memory device*.'" Appx6951-52 (emphasis added). When "only one rank is selected," it urged, "the command signal will be sent to only a single memory device"—the single device in the rank. Appx6952. The Examiner reiterated that Amidi did not teach what claim 16 required—"transmit[ting] a command signal to only one DDR memory device at a time *when there is a plurality of memory devices in a rank*." Appx7337 (emphasis added).

2. The Board upheld the Examiner's decision. Claim 16, it held, "'require[s] transmission of a command signal to only one DDR memory device at a time '"—*i.e.*, "'*to only one DDR memory device at a time when there is a plurality*

16

*of memory devices in a rank*.'" Appx10561 (emphasis altered). Because Amidi taught that signals were transmitted to "*multiple* memory devices at a time," it did not render claim 16 obvious. Appx10561. However, the Board remanded to the Examiner for consideration of new grounds as to certain claims. Appx9614; Appx10032. The Board denied rehearing on all the claims it had upheld. Appx10647.

3. The patent was then subjected to a *second* round of reexamination in the same proceeding. Appx9788-89. A second appeal to the Board followed, which found that the prior decision to uphold claim 16 "remains affirmed." Appx10251. The Board again denied rehearing. Appx10373-84.

Requesters appealed, challenging the Board's decision to uphold claim 16. See Inphi.Br.48-49 in Google LLC v. Netlist, Inc., No. 19-1720 (Fed. Cir.). This Court affirmed without opinion. Google LLC v. Netlist, Inc., 810 F. App'x 902 (Fed. Cir. 2020).

#### **III. PROCEDURAL HISTORY**

This is the fourth post-grant attempt to invalidate claim 16. After the prior attempts by Google and others failed, Samsung initiated this IPR. This time, the Board concluded claim 16 was obvious. The Board, however, pointed to no material difference in the asserted prior art—it relied on a reference the Examiner considered during initial examination. Instead, the Board adopted a new construction of claim 16 that contradicted the construction the Examiner and Board had adopted in upholding claim 16 during reexamination.

## A. Samsung's Petition

Samsung's Petition invoked three putative prior-art references: Ellsberry, Amidi, and Perego-422. Netlist urged the Board to deny the Petition as cumulative and abusive. Ellsberry and Amidi were considered during initial examination—they are listed on the face of the '912 patent—and Perego-422 is similar to another Perego reference considered during prosecution. Appx295-96. Samsung, moreover, was Google's main supplier of infringing memory modules and had been aware of the earlier reexamination but chose not to participate. Appx296-301. The Board instituted review nonetheless. Appx482-89.

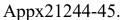

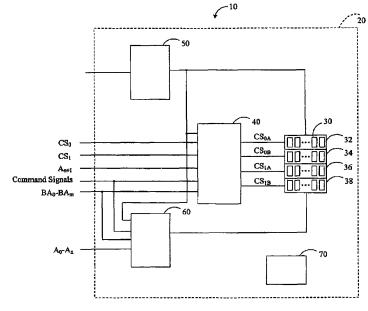

The Board relied only on Ellsberry, an abandoned patent application, No. 2006/0277355, filed June 1, 2005 and published December 7, 2006. Appx52. Ellsberry teaches "expand[ing] the addressable memory banks on a module by making two smaller-capacity memory devices emulate a single higher-capacity memory device." Appx11904-05 (¶26). Ellsberry incorporates the JEDEC standard (in part) by reference and aims to "comply with industry standards." Appx11903 (¶9); Appx11908 (¶50).

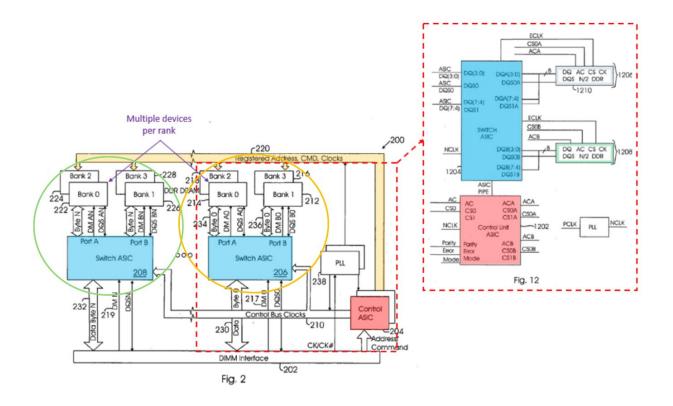

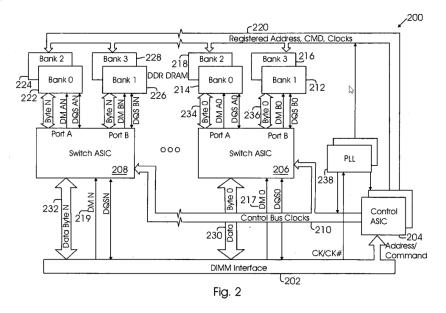

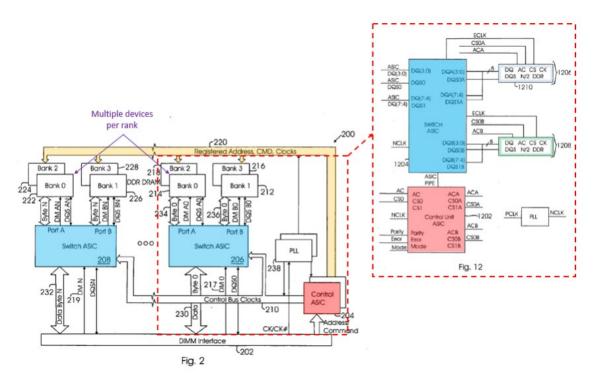

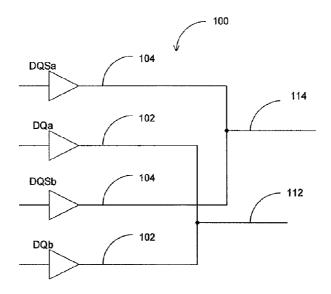

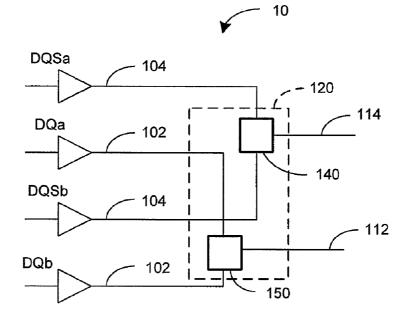

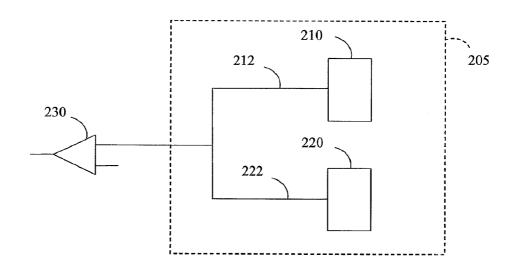

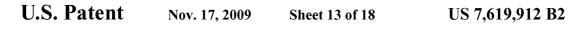

As shown in Ellsberry's Figure 2, Ellsberry's memory system uses a control unit 204 (blue box) and multiple switches 206 and 208 (red boxes) to control a

18

number of memory chips (212, 214, 216, 218, 222, 224, 226, 228, green box). Appx11903-06(¶¶28-29, 35). The control unit receives "address and command" signals from the computer's memory controller (through interface 202), and outputs address and command signals (transmitted through wires 220) to control the memory chips. Appx11906(¶39).

Appx11885 (annotated).

In Ellsberry, memory chips are organized into "banks" (mapped by the Petition to the claimed "ranks"). Appx11906(¶35) (Ellsberry); Appx202 (Petition). In the image above, there are four banks, "Bank 0" through "Bank 3," each including multiple memory chips. Appx11905(¶30). For example, "Bank 1" includes memory chips 212 and 226, while "Bank 2" includes memory chips 218 and 224.

Appx11905(¶30). Ellsberry undisputedly sends command signals to all DRAM devices in each rank at the same time. Appx11905(¶30).

Each "switch ASIC" and its associated memory chips also constitute a "data group." Appx11905( $\P$ 30). As shown above, Ellsberry's memory module features a plurality of data groups—two shown in the image above, with ellipses (yellow box) indicating there are more that are not shown. Appx11905( $\P$ 30).

#### **B.** The Board's Final Written Decision

The Board determined that claim 16 was obvious in view of Ellsberry.

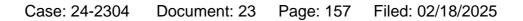

1. Whether Skilled Artisans Would Understand Claim 16's "Ranks" Necessarily Include Multiple DRAM Chips

The Board addressed whether Ellsberry discloses "per DRAM addressability"—*i.e.*, that command signals can be sent "to *only one* memory device" as claim 16 requires. Appx84(8:50-54) (emphasis added); Appx105(7:20-24). The Board did not find that Ellsberry teaches or suggests "transmitting [a] command signal" to "*only one* DDR memory device at a time" in a rank having a plurality of memory devices. Appx50 (emphasis added); *see* Appx103(3:35-36, 42-43). To the contrary, it was undisputed that in Ellsberry, signals are sent to *all* the DDR memory devices in a "bank" (which the Board equated with claim 16's "rank"); if there are four DDR devices in a rank, all four get the command. *See* Appx140.

The Board thus posited that "the dispositive issue for claim construction" is "whether 'rank' can include just '*one* memory device.'" Appx14 (emphasis added). Ellsberry, the Board stated, disclosed sending commands to a single *bank* (rank) at a time. Appx43. The Board asserted that, *if each bank in Ellsberry has only a single chip*, then sending a command to an entire bank at a time would teach or suggest claim 16's requirement of sending commands to a single chip at a time. Appx46-50. (As explained below, the Board determined that Ellsberry also disclosed ranks that have just "one memory device." Appx50.)

The Board rejected Netlist's argument that "*claim 16 requires* sending a command to a single device that is *in a multi-device rank*." Appx51 (emphasis added). The Board never disputed that, in issuing claim 16, the Examiner and the Board previously agreed with Netlist that the claims require sending "'a command signal to only one DDR memory device at a time *when there is a plurality of memory devices in a rank*." Appx10561 (emphasis modified); *see* pp. 15-17, *supra*. Nor did the Board dispute that skilled artisans reading that intrinsic record would understand that claim 16 requires sending the command to one device in a multidevice rank. But the Board, without explanation, dismissed that prosecution history—reflecting the Board's and Netlist's express understanding of the claim's scope—as erroneous. The "reexamination," it declared, "do[es] not elucidate the proper construction of 'rank.'" Appx23.

The Board also rejected Netlist's reliance on claim 16's text. Appx15. Claim 16, Netlist urged, addressed "a type of memory *standardized by JEDEC*."

21

Appx950-51 (emphasis added). JEDEC DDR standards required memory modules to read/write 64 or 72 bits at a time, but JEDEC-compliant memory chips were only 4, 8, or 16 bits. Appx952. Consequently, Netlist argued, skilled artisans would understand claim 16's "rank" must contain multiple memory chips working together to meet the overall module's bit-width requirement. Appx952; pp. 7-9, *supra*. The Board, however, merely re-asserted, without explanation, that claim 16 "does not preclude the possibility that a rank could have a single memory device." Appx15.

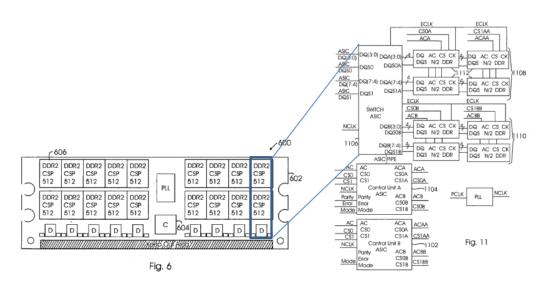

The Board indicated that the '912 patent's specification does not explicitly state that a rank must include multiple memory devices. Appx18. It did not dispute that skilled artisans reading claim 16's prosecution history—including the Examiner's and its own prior statements—would understand that claim 16 is limited to multi-device ranks. Instead, it cited three instances in the specification, Table 1, Figure 6B, and Example 2, that it believed could include a single-device rank. Appx15-23. It did not explain why those three instances—even if they *could* include a single-device rank—would overcome an artisan's understanding that claim 16 complied with JEDEC standards or the prosecution history.

### 2. Priority from the '436 Patent and the '244 Provisional

The Board also rejected Netlist's arguments that Ellsberry was not prior art because the '912 patent was entitled to an earlier priority date. Appx30. The '912 patent, Netlist urged, was entitled to the earlier priority dates of U.S. Patent No.

22

7,286,436 ("the '436 patent") or U.S. Provisional 60/588,244 ("the '244 provisional"). Appx30.<sup>1</sup>

<u>The '436 Patent</u>. The '912 patent claims priority from the '436 patent. *See* Appx25. The Board held that, although the '436 patent predates Ellsberry, it lacks written-description support for the "register" required by limitation 16[c]. Appx31-32. The Board nowhere denied that registers were commonplace when the '436 patent was filed—or that patents need not disclose what is known in the art. But it rejected Netlist's argument that skilled artisans would understand that the '436 patent's "programmable-logic device (PLD) 642" contains a register. Appx30. Netlist pointed out that the programmable logic device performs "sequential logic" and thus must "include a register to store state values." Appx30. Both parties' experts agreed that skilled artisans would recognize that sequential logic requires "a *register* or an equivalent" device. Appx18693-94(117:16-118:20) (Samsung's expert) (emphasis added); Appx18345-46(¶78) (Netlist's expert).

The Board nonetheless held that the '436 patent does not describe a register because it does not "mention" a "register." Appx31. The Board acknowledged the expert consensus that skilled artisans would recognize that the reference to

<sup>&</sup>lt;sup>1</sup> The Board also found Ellsberry was a prior-art "printed publication" that could be considered in an IPR under 35 U.S.C. §311(b), even though Ellsberry, a patent application that never issued as a patent, was not public as of the '912 patent's latest possible priority date. Appx35.

sequential logic requires a register or equivalent device. Appx31. But the Board declared that "other types of devices, such as flip-flops and memory" could perform the same function. Appx31. For the latter determination, the Board invoked a *2024* website the Board had found on its own. *See* Appx1583. The Board did not explain how that could somehow reflect a skilled artisan's understanding in 2005.

Although no party requested construction of the "register" limitation, the Board *sua sponte* ruled that the '912 patent's "logic element" and the "register" must be "two different things." Appx31-32. Based on that construction, it ruled that the '436 patent's register did not support claim 16, because the '436 patent describes any register as "included in the logic element." Appx31-32. The Board did not mention the '912 patent's disclosure that the "logic element" and the "register" can be "portions of a single component." Appx83(5:37-43).

Finally, the Board faulted Netlist for addressing written-description support only for "'each disputed limitation,' i.e., those raised by Petitioner." Appx33. To establish priority, the Board asserted, Netlist had to discuss "all limitations of claim 16," even those that were undisputed. Appx33-34. The Board did not mention Board precedent holding that a patent owner's written-description showing need only be "commensurate in scope with the specific points and contentions raised by the petitioner." *See, e.g., Lupin Ltd. v. Pozen, Inc.*, IPR2015-01775, Paper 15, at 10-11 (PTAB Mar. 1, 2016); Appx1537. <u>The '244 Provisional</u>. The '912 patent independently claims priority from the '244 provisional, which also predates Ellsberry. Appx25. The Board held that the '244 provisional did not provide written-description support for a "bank address signal" as limitation 16[c] requires. Appx26-30.

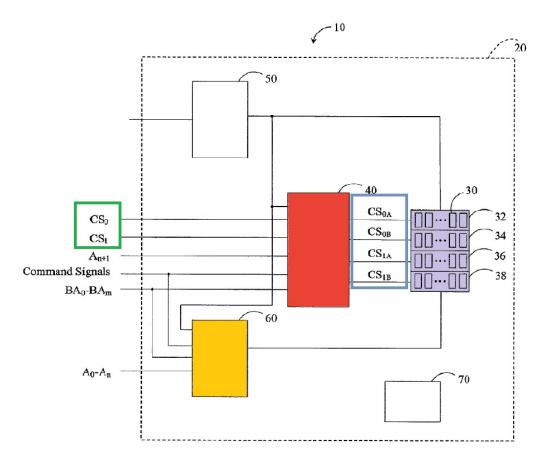

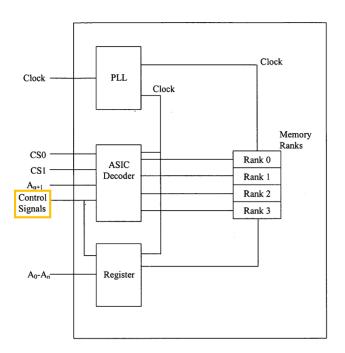

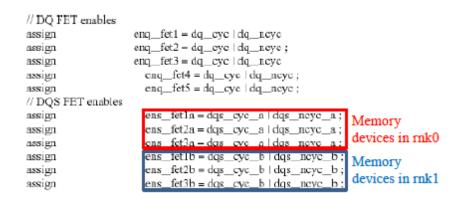

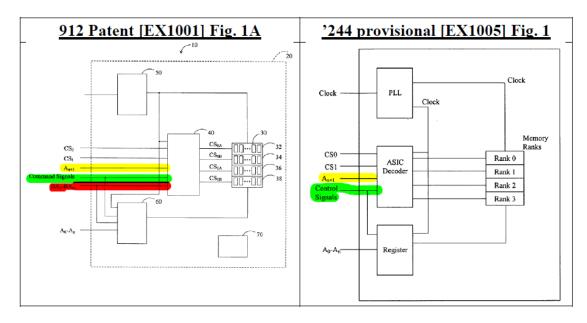

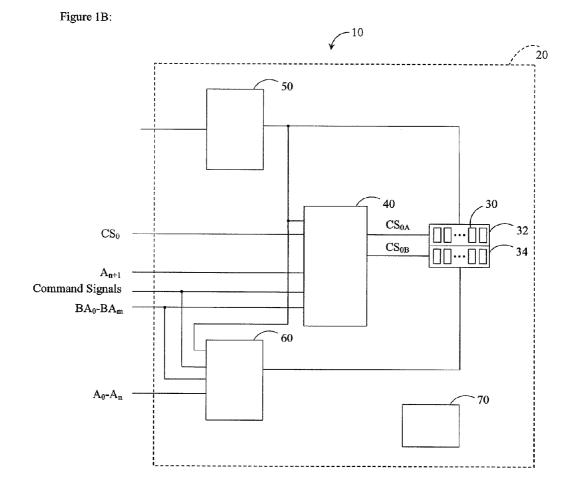

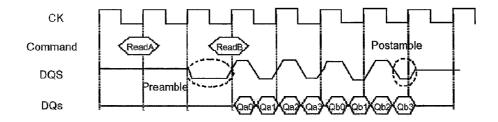

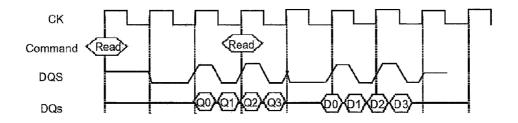

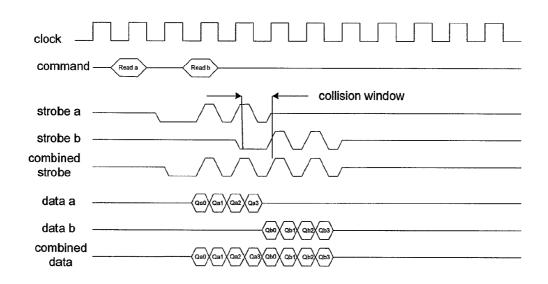

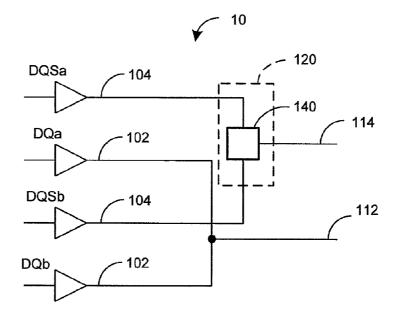

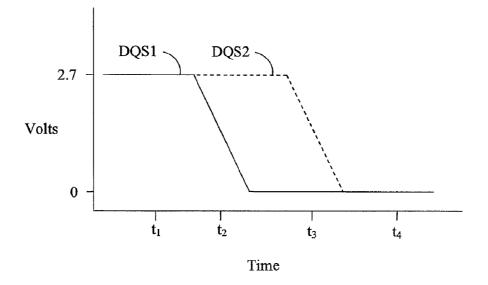

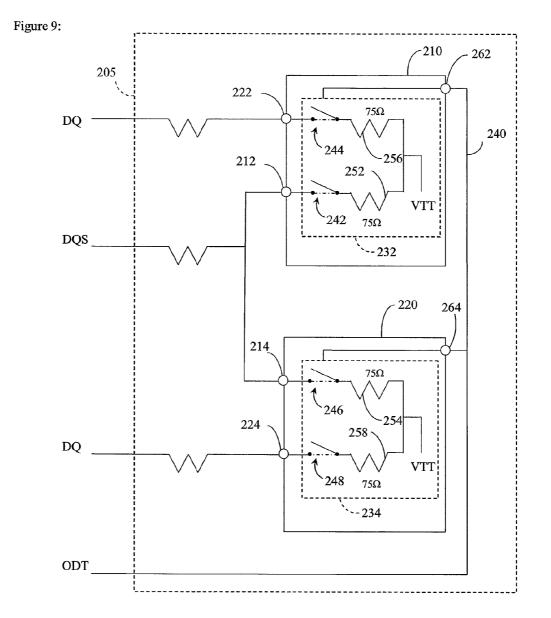

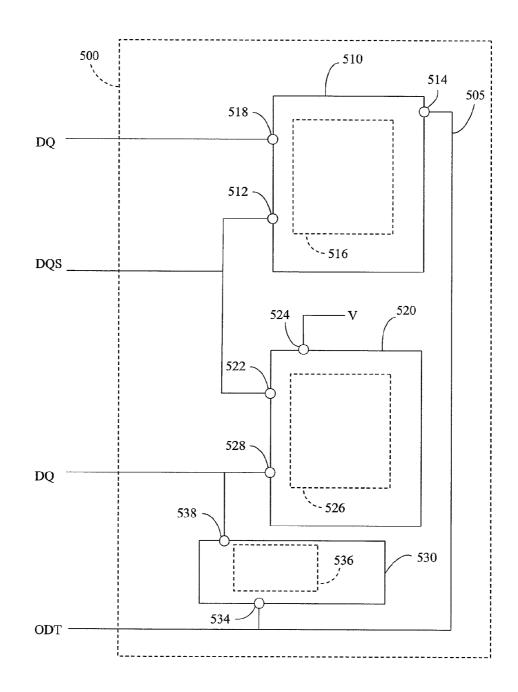

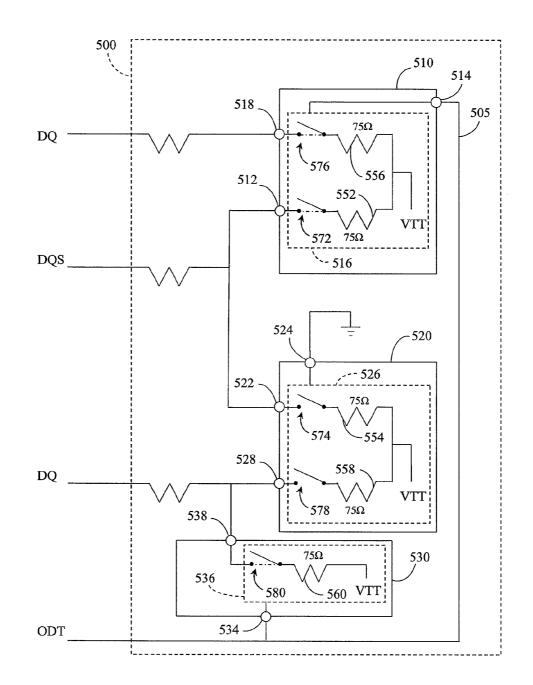

The Board did not dispute that "bank address signals" were, at the time of the '244 provisional, well known. In addition, limitation 16[c] requires a "logic element" to receive a "set of input signals from the computer system," including "bank address signals." Appx103(3:17-21). The '244 provisional does not use the term "bank address signals," but does disclose "control signals," as shown in Figure 1:

Appx2344 (annotated). Under then-applicable JEDEC standards for DRAM memory modules, "control signals" *necessarily* included bank address signals.

Appx18313-19( $\P$ 62-64). Without bank address signals, basic operations like "read" and "write" would not work—without knowing the bank, the memory module could not locate the cell it wants to read from or write to. Appx18315-16( $\P$ 63).

In the relevant timeframe, Netlist pointed out, "'**90%** of DRAM production [was] in compliance with the [JEDEC DDR] standards.'" Appx1263 (quoting *Rambus Inc. v. FTC*, 522 F.3d 456, 459-61 (D.C. Cir. 2008)) (emphasis added). Indeed, the first page of the '244 provisional refers to "personal computer[s]." Appx2283(¶1). As Samsung's expert confirmed, skilled artisans would understand that to mean JEDEC-compliant memory devices. Appx18649(73:9-15). Netlist also presented evidence that the '244 provisional uses "specific terminology" indicating that its memory module is a "JEDEC-style memory module"—for example, referring to JEDEC standard chip-select signals "CS0 and CS1," and using the term "rank," which JEDEC created. Appx18313-14(¶60).

The Board did not engage with that evidence on the merits. Instead, it ruled that, to find written-description support for bank address signals, skilled artisans would have to make a "chain" of "inferences": (1) "that the '244 provisional pertains to DDR memory modules"; (2) "that DDR DRAMs use bank address signals according to the JEDEC standards"; (3) "that bank address signals are not mentioned in the '244 provisional"; (4) "that bank address signals would be included as part of the control signals"; and (5) "that the bank address signals are used for rank multiplica-

tion." Appx29-30. The Board deemed that "chain of inferences too long and speculative" to conclude the inventors possessed the "bank address" limitation. Appx30. The Board did not acknowledge that the second through fourth steps were undisputed. Nor did it mention that its fifth step—using bank address signals for rank multiplication—was not a claim requirement. And that step was disclosed regardless.

#### **SUMMARY OF ARGUMENT**

I. Limitation 16[e] requires "transmitting [a] command signal" to a memory device in a selected "rank[]," "wherein the command signal is transmitted to *only one DDR memory device* at a time." Ellsberry teaches sending commands to every memory device in a rank "*simultaneously*." Appx1021 (emphasis added); *see* Appx1551. To find limitation 16[e] satisfied, the Board construed it to cover sending a command to *all* memory devices in a putative "rank" that includes just *one* memory device. Appx14.

A-B. The Board's construction defies the prosecution history, the Board's own prior construction, and a disclaimer. During reexamination, the Examiner construed claim 16 to require sending a command to "only one DDR memory device at a time *when there is a plurality of memory devices in a rank*." The Board and this Court affirmed. The Board in this case was not free to disregard that history. The claims, moreover, recite JEDEC's "DDR" standard, which precludes single-

device ranks. The specification, which cites JEDEC's standards, uniformly provides for ranks having more than one memory device. The Board's contrary decision improperly defies the intrinsic evidence and its own prior decisions. Even if the Board were not bound by its prior construction, the APA required it to explain why it reached the opposite result here. The Board failed to do that.

C. The Board's construction attempts to interpret "rank" in the abstract rather than in the context of the claims, specification, and prosecution history. Claim differentiation cannot support the Board's decision, much less override prosecution history. And the Board misapprehended the specification—erroneously concluding that abbreviated examples that illustrate operational details somehow show that claim 16's ranks can have just one memory device.

II. Even if sending a command to a single-device "rank" could satisfy claim 16, Ellsberry does not teach single-device ranks. The Board pointed to Ellsberry's Figure 12, but misunderstood what that figure shows—*part* of a rank, not an entire rank with just one memory device. The Board recognized that aspect of Ellsberry in a prior IPR, but it again ignored its earlier decision here.

III. The Board's determination that Ellsberry is prior art to the '912 patent cannot be sustained because the patent claims priority to *two* filings that antedate Ellsberry.

#### Case: 24-2304 Document: 23 Page: 42 Filed: 02/18/2025

A. The '912 patent is entitled to priority from Netlist's '436 patent. The Board asserted that the '436 patent does not disclose a "register." But registers were well known at the time. And there was no dispute that skilled artisans would recognize the '436 patent's disclosure of "sequential logic" to require a "register or an equivalent" device. That constitutes disclosure. The Board's *sua sponte* ruling that the "register" and "logic element" must be "two different things," Appx31, was both improper and plainly wrong. And the Board's insistence that Netlist should have addressed undisputed limitations contravenes its own precedent.

B. The '912 patent is also entitled to priority from the '244 provisional. The Board ruled that the '244 provisional does not disclose "bank address signals." Appx29-30. But bank address signals were well known at the time of the '912 patent. And it was undisputed that the '244 patent discloses "control signals," which the JEDEC standards required to contain bank address signals. The Board's response—that the '244 provisional might not be referring to JEDEC-compliant memory devices—defies precedent and the unrebutted evidence. And the Board's reference to a "chain" of five "speculative" inferences, Appx30, overlooks that four of the five were effectively undisputed or irrelevant.

C. Ellsberry was not a "patent[]" or a "printed publication[]" on the '912 patent's critical date and thus is not prior art under 35 U.S.C. §311(b).

#### **STANDARD OF REVIEW**

Obviousness is a question of law, reviewed de novo; underlying factfindings are reviewed for substantial evidence. *Virtek Vision Int'l ULC v. Assembly Guidance Sys., Inc.*, 97 F.4th 882, 886 (Fed. Cir. 2024). Claim construction is reviewed de novo, including the Board's evaluation of intrinsic evidence. *Intel Corp. v. Qualcomm Inc.*, 21 F.4th 801, 808 (Fed. Cir. 2021). Sufficiency of written description is reviewed for substantial evidence, but the Board's interpretation of precedent regarding the written-description requirement is reviewed de novo. *Falkner v. Inglis*, 448 F.3d 1357, 1362 (Fed. Cir. 2006). Board decisions must be vacated if they are "arbitrary, capricious, an abuse of discretion," "not in accordance with law," or "unsupported by substantial evidence." *Pers. Web Techs., LLC v. Apple, Inc.*, 848 F.3d 987, 992 (Fed. Cir. 2017).

#### ARGUMENT

It is said that doing the same thing over and over again, while expecting different results, is the definition of insanity. For challengers to Netlist's patent, however, it turned out to be sound litigation strategy. Netlist's '912 patent has been subject to post-grant challenge after post-grant challenge. Almost immediately upon issuance, it was hit with three inter partes reexaminations by Google and others. Over the ensuing decade, those reexaminations generated over a dozen asserted grounds of unpatentability, twenty-plus briefs, five office actions, two appeals to the

Board, and an appeal to this Court. When the dust settled, the Examiner and the Board upheld the patent's claim 16, and this Court affirmed. *Google LLC v. Netlist, Inc.*, 810 F. App'x 902 (Fed. Cir. 2020). But the ordeal continued. Samsung, Google's supplier of infringing memory devices, continued the campaign against claim 16 by filing this IPR—the fourth administrative challenge to the claim. And *this* time, the Board declared claim 16 unpatentable.

Did Samsung discover some previously unknown, silver-bullet prior art? No. The Board's decision rested entirely on Ellsberry, a reference listed on the face of the '912 patent and considered during initial examination. The Board justified invalidating claim 16 this time based on a claim construction *directly contrary* to the construction that the Board and the Examiner previously adopted—and Netlist accepted—in the prior reexaminations. The Board never explained why it could disregard that part of the intrinsic record—or why skilled artisans would ignore that powerful evidence of meaning in reading the claims.

That is not how claim construction—or administrative law—is supposed to work. The PTO is not a casino where patent challengers can keep pulling the slot machine, in hopes that the *next* Board panel will turn up their desired result. A patent claim does not change meaning from proceeding to proceeding or from panel to panel. That is especially true where, as here, the Examiner and Board adopt a claim construction and the patent owner agrees to that construction: Those representations effect a disclaimer of alternative constructions that is *binding* on the patentee and the Board alike.

Those principles foreclose the Board's about-face here. In the prior reexaminations, the Examiner and Board construed claim 16 to require *multiple* memory devices in a rank: The claim, they ruled, requires transmission of a command signal "to only one DDR memory device at a time *when there is a plurality of memory devices in a rank*." Appx7337, Appx10561 (emphasis added). Netlist accepted that construction, not merely by defending the Examiner's decision before the Board, but also by restating claim 16 in light of that construction. That constituted a clear disclaimer of single-device ranks, which the Board was not free to disregard. Yet it did precisely that below. This time, the Board held claim 16 *does* encompass singledevice ranks. And it ruled that Ellsberry rendered the claim obvious because it (purportedly) disclosed sending a command signal to only one DDR memory device at a time *if* there was only one memory device in a rank.

The defects with the Board's decision run deeper still. The Board's newly minted construction defies the claim language and specification, as well as the industry standards they incorporate. Ellsberry does not teach what the Board professed to find in it. And Ellsberry is not even prior art: Netlist antedated it with *two* filings that disclose claim 16's invention.

#### I. THE BOARD'S RULING THAT CLAIM 16 COVERS A "RANK" HAVING ONLY ONE DRAM DEVICE REQUIRES REVERSAL

Claim 16 requires "transmitting [a] command signal to at least one DDR memory device of [a] selected one or two *ranks*," "wherein the command signal is transmitted to *only one DDR memory device* at a time." Appx103(3:35-43) (emphasis added) (limitations 1[c] & [e]). There was no dispute Ellsberry teaches sending commands to *every* DRAM device in a rank "*simultaneously*." Appx1021 (emphasis added); *see* Appx1551. That is the opposite of selectively sending commands "to only one DDR memory device at a time." To find limitation 16[e] satisfied none-theless, the Board construed that limitation to cover sending commands to *all* memory devices in a "rank" where the rank happens to "include only one memory device." Appx14.

That construction directly contradicts the Board's *own* construction when claim 16 was issued; it defies the prosecution history; it contravenes the claim's text; and it makes no sense. During a lengthy reexamination, the Examiner construed original dependent claim 16 (now limitation 16[e]) to require "'transmit[ting] a command signal to only one DDR memory device at a time *when there is a plurality of memory devices in a rank*.'" Appx6375 (emphasis added); *see* Appx7231; Appx7337; Appx7494. The Examiner understood claim 16 only applies to—and only makes sense in the context of—ranks that have more than one memory device. Netlist disclaimed any construction that would cover sending commands to all

devices in a rank, merely because a rank may have one device in it. The Board in turn agreed that claim 16 requires "'transmit[ting] a command signal *to only one DDR memory device at a time when there is a plurality of memory devices in a rank*," upholding the claim in the reexamination on that basis. Appx10561 (emphasis Board's). And this Court affirmed. *Google LLC v. Netlist, Inc.*, 810 F. App'x 902 (Fed. Cir. 2020).

That history forecloses the Board's effort to impose the opposite construction here. The meaning of a claim does not change simply because there is yet another challenge before a different PTAB panel. More fundamentally, the Examiner's and Board's prior construction is part of the intrinsic evidence to which skilled artisans would look to determine the claim's scope. The Board never explained why the Patent Office's own view of the claim during the reexamination—when claim 16 issued—would not be determinative to any reader of the intrinsic record. Indeed, Netlist accepted that construction, disclaiming a broader scope. Reversal must follow.<sup>2</sup>

<sup>&</sup>lt;sup>2</sup> All the Petition's combinations urge that claim 16 is obvious in view of prior art involving single-device ranks. Appx189-91; Appx237-39. If limitation 16[e] requires the capability to transmit a command signal to a single device in a multi-device rank, the Petition fails on all grounds.

# A. Claim 16 Covers Sending Commands to Only One DRAM Among Multiple DRAMs in a Rank—Not Sending a Command to *Every* DRAM in a "Rank" That Happens To Have Only One DRAM

Claim construction "seeks to accord a claim the meaning it would have to a person of ordinary skill in the art at the time of the invention." *Innova/Pure Water, Inc. v. Safari Water Filtration Sys., Inc.*, 381 F.3d 1111, 1116 (Fed. Cir. 2004). That requires looking to the entire intrinsic record, including "the written description and the prosecution history." *Phillips v. AWH Corp.*, 415 F.3d 1303, 1313 (Fed. Cir. 2005) (en banc). This Court thus has warned against looking at "ordinary meaning ... in a vacuum," or fixating on the "abstract meaning of words rather than on the meaning of claim terms within the context of the patent." *Id.* at 1313, 1321.

Here, the Board strained to give claim 16 an expansive meaning that, in view of the invention's nature and prosecution history, it simply cannot bear. The whole point of the invention—of individual DRAM-chip addressability—is to send a command to one device in a rank without sending it to the other devices in the rank. Claim 16 thus provides for "transmitting [a] command signal to at least one DDR memory device of [a] selected one or two *ranks*," wherein "the command signal is transmitted to *only one DDR memory device* at a time." Appx103(3:35-43) (emphasis added) (limitations 1[c] & [e]). That language, by its terms, refers to sending the command to only one of the multiple memory devices in a rank—not

broadcasting it to every memory device in the rank when it just so happens the rank allegedly has only one device.

The prosecution history makes that undisputable. Prosecution history, 1. "'including reexamination proceedings," Infinity Comput. Prods., Inc. v. Oki Data Am., Inc., 987 F.3d 1053, 1059 (Fed. Cir. 2021) (emphasis added), is "intrinsic evidence" for claim construction, Elkay Mfg. Co. v. Ebco Mfg. Co., 192 F.3d 973, 977 (Fed. Cir. 1999). And where, as here, the patentee "disavowed a potential interpretation of" the claim "during prosecution" by accepting the "Examiner's" construction, that disavowal is binding in subsequent proceedings, *including on the* **Board**. Elkay, 192 F.3d at 979; see Biogen Idec, Inc. v. GlaxoSmithKline LLC, 713 F.3d 1090, 1095 (Fed. Cir. 2013). The "Board in an inter partes review *can[not]* ignore statements made in a prior reexamination," and "must 'exclude any interpretation that was disclaimed." VirnetX Inc. v. Mangrove Partners Master Fund, Ltd., 778 F. App'x 897, 910 (Fed. Cir. 2019) (emphasis added); see Arendi S.A.R.L. v. Google LLC, 882 F.3d 1132, 1136 (Fed. Cir. 2018).

Here, limitation [e] of independent claim 16 was dependent claim 16 before the reexamination. Appx97(34:57-59); *see* pp. 14-16, *supra*. In the reexamination, the Examiner upheld claim 16 over a prior-art reference, Amidi, by construing the claim to require "only one DDR memory device at a time *when there is a plurality of memory devices in a rank*." Appx6375 (emphasis added). Amidi taught sending commands "to *all devices*" in a rank—regardless of how many there were—and thus did not teach the claim. Appx6413 (emphasis added). It thus was irrelevant whether Amidi theoretically could send commands to only one device at a time where the "rank" had only "one memory device." Appx6911. A command in Amidi would *not* be sent to just one memory device "when there is a plurality of memory devices in a rank," as claim 16 requires. Appx7231. Netlist accepted the construction by canceling independent claim 15 and restating claim 16 to incorporate the limitations of original claim 15 while retaining the requirement of original dependent claim 16 that the Examiner had upheld. Appx5615-16.

The Board upheld the Examiner. Appx10560-61. It agreed that claim 16 requires "'transmit[ting] a command signal *to only one DDR memory device at a time when there is a plurality of memory devices in a rank*.'" Appx10561 (emphasis Board's). The Board ruled that Amidi did not teach that requirement, because it taught the conventional approach of sending a command to all "memory *devices*" in a rank. Appx10561-62 (emphasis Board's). Like the Examiner, the Board did not deny the possibility that a rank in Amidi could include only one memory device, such that sending a command to all memory devices in a rank would entail sending a command to only one memory device. *See* Appx6911. Indeed, one of the requesters argued that Amidi disclosed precisely that. *See* p. 16, *supra*. But that could not satisfy claim 16, which requires sending a command signal "'to only

one DDR memory device at a time *when there is a plurality of memory devices in a rank*.'" Appx10561 (some emphasis omitted). This Court affirmed. *Google LLC v. Netlist, Inc.*, 810 F. App'x 902 (Fed. Cir. 2020).