No. 2024-2304

# IN THE UNITED STATES COURT OF APPEALS FOR THE FEDERAL CIRCUIT

NETLIST, INC., *Appellant*,

v.

SAMSUNG ELECTRONICS CO., LTD., MICRON TECHNOLOGY INC., MICRON SEMICONDUCTOR PRODUCTS, INC., MICRON TECHNOLOGY TEXAS, LLC,

Appellees.

Appeal from the United States Patent and Trademark Office, Patent Trial and Appeal Board in Nos. IPR2022-00615, IPR2023-00203

### APPELLEES' RESPONSE BRIEF

May 30, 2025

E. Joshua Rosenkranz

Emily W. Villano

ORRICK, HERRINGTON &

SUTCLIFFE LLP

51 West 52nd Street

New York, NY 10019

(212) 506-5000

Michael Hawes

Lori Ding

BAKER BOTTS L.L.P.

910 Louisiana Street

Houston, TX 77002

(713) 229-1234 (telephone)

michael.hawes@bakerbotts.com

lori.ding@bakerbotts.com

Counsel for Micron Technology, Inc., Micron Semiconductor Products, Inc., Micron Technology Texas, LLC

Counsel for Samsung Electronics Co., Ltd.

Additional counsel listed on inside cover

Melanie L. Bostwick Robbie Manhas Orrick, Herrington & Sutcliffe LLP 2100 Pennsylvania Avenue, NW Washington, DC 20037

Jared Bobrow

ORRICK, HERRINGTON &

SUTCLIFFE LLP

1000 Marsh Road

Menlo Park, CA 94025

Counsel for Micron Technology, Inc., Micron Semiconductor Products, Inc., Micron Technology Texas, LLC Eliot Williams

BAKER BOTTS L.L.P.

700 K Street, NW

Washington, DC 20001

(202) 639-7700 (telephone)

eliot.williams@bakerbotts.com

Theodore W. Chandler BAKER BOTTS L.L.P. 1801 Century Park East, Suite 2400 Los Angeles, CA 90067 (213) 202-5702 (telephone) ted.chandler@bakerbotts.com

Counsel for Samsung Electronics Co., Ltd.

### PATENT CLAIM LANGUAGE AT ISSUE

### U.S. Patent No. 7,619,912

### Original Claims 15 & 16 (Appx97) Challenged Claim 16 (Appx103)

**15.** A memory module connectable to a computer system, the memory module comprising:

a printed circuit board;

a plurality of double-data-rate (DDR) memory devices coupled to the printed circuit board,

the plurality of DDR memory devices having a first number of DDR memory devices arranged in a first number of ranks;

a circuit coupled to the printed circuit board, the circuit comprising a logic element and a register,

the logic element receiving a set of input signals from the computer system, the set of input signals comprising at least one row/column address signal, bank address signals, and at least one chip-select signal,

the set of input signals configured to control a second number of DDR memory devices arranged in a second number of ranks, the second number of DDR memory devices smaller than the first number of DDR memory devices and the second number of ranks less than the first number of ranks,

**16.** [16.pre] A memory module connectable to a computer system, the memory module comprising:

[16.a] a printed circuit board;

[16.b] a plurality of double-data-rate (DDR) memory devices coupled to the printed circuit board,

[16.b.i] the plurality of DDR memory devices having a first number of DDR memory devices arranged in a first number of ranks;

[16.c] a circuit coupled to the printed circuit board, the circuit comprising a logic element and a register,

[16.c.i] the logic element receiving a set of input signals from the computer system, the set of input signals comprising at least one row/column address signal, bank address signals, and at least one chip-select signal,

[16.c.ii] the set of input signals configured to control a second number of DDR memory devices arranged in a second number of ranks, the second number of DDR memory devices smaller than the first number of DDR memory devices and the second number of ranks less than the first number of ranks,

### Original Claims 15 & 16 (Appx97)

the circuit generating a set of output signals in response to the set of input signals, the set of output signals configured to control the first number of DDR memory devices arranged in the first number of ranks,

wherein the circuit further responds to a command signal and the set of input signals from the computer system by selecting one or two ranks of the first number of ranks and transmitting the command signal to at least one DDR memory device of the selected one or two ranks of the first number of ranks; and

a phase-lock loop device coupled to the printed circuit board,

the phase-lock loop device operatively coupled to the plurality of DDR memory devices, the logic element, and the register.

**16.** The memory module of claim 15, wherein the command signal is transmitted to only one DDR memory device at a time.

### Challenged Claim 16 (Appx103)

[16.c.iii] the circuit generating a set of output signals in response to the set of input signals, the set of output signals configured to control the first number of DDR memory devices arranged in the first number of ranks,

[16.c.iv] wherein the circuit further responds to a command signal and the set of input signals from the computer system by selecting one or two ranks of the first number of ranks and transmitting the command signal to at least one DDR memory device of the selected one or two ranks of the first number of ranks; and

[16.d] a phase-lock loop device coupled to the printed circuit board,

[16.d.i] the phase-lock loop device operatively coupled to the plurality of DDR memory devices, the logic element, and the register,

[16.e] wherein the command signal is transmitted to only one DDR memory device at a time.

FORM 9. Certificate of Interest

Form 9 (p. 1) March 2023

### UNITED STATES COURT OF APPEALS FOR THE FEDERAL CIRCUIT

### CERTIFICATE OF INTEREST

| Case Number               | 2024-2304                                      |

|---------------------------|------------------------------------------------|

| <b>Short Case Caption</b> | Netlist, Inc. v. Samsung Electronics Co., Ltd. |

| Filing Party/Entity       | Samsung Electronics Co., Ltd.                  |

#### **Instructions:**

- 1. Complete each section of the form and select none or N/A if appropriate.

- 2. Please enter only one item per box; attach additional pages as needed, and check the box to indicate such pages are attached.

- 3. In answering Sections 2 and 3, be specific as to which represented entities the answers apply; lack of specificity may result in non-compliance.

- 4. Please do not duplicate entries within Section 5.

- 5. Counsel must file an amended Certificate of Interest within seven days after any information on this form changes. Fed. Cir. R. 47.4(c).

I certify the following information and any attached sheets are accurate and complete to the best of my knowledge.

| Date: <u>09/25/2024</u> | Signature: | /s/ Michael Hawes |

|-------------------------|------------|-------------------|

|                         | Name:      | Michael Hawes     |

| 1. Represented Entities. Fed. Cir. R. 47.4(a)(1).                                       | 2. Real Party in<br>Interest.<br>Fed. Cir. R. 47.4(a)(2).                                                                                   | 3. Parent Corporations<br>and Stockholders.<br>Fed. Cir. R. 47.4(a)(3).                                                                        |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Provide the full names of all entities represented by undersigned counsel in this case. | Provide the full names of all real parties in interest for the entities. Do not list the real parties if they are the same as the entities. | Provide the full names of all parent corporations for the entities and all publicly held companies that own 10% or more stock in the entities. |

|                                                                                         | ☐ None/Not Applicable                                                                                                                       | ☑ None/Not Applicable                                                                                                                          |

| Samsung Electronics Co., Ltd.                                                           | Samsung Semiconductor, Inc.                                                                                                                 |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

$\square$  Additional pages attached

Casse: 224-223004 | Document: 36 | Page: 37 | Filed: 0095/250/2002/5

FORM 9. Certificate of Interest

Form 9 (p. 3) March 2023

| <b>4. Legal Representatives.</b> List all law firms, partners, and associates that (a) appeared for the entities in the originating court or agency or (b) are expected to appear in this court for the entities. Do not include those who have already entered an appearance in this court. Fed. Cir. R. 47.4(a)(4).                                                                                                                                  |                                       |                                   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------|--|

| ☐ None/Not Applicable                                                                                                                                                                                                                                                                                                                                                                                                                                  | ☐ Additi                              | onal pages attached               |  |

| Brianna Potter<br>Baker Botts L.L.P.                                                                                                                                                                                                                                                                                                                                                                                                                   | Ferenc Pazmandi<br>Baker Botts L.L.P. | Eric Faragi<br>Baker Botts L.L.P. |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |                                   |  |

| <ul> <li>5. Related Cases. Other than the originating case(s) for this case, are there related or prior cases that meet the criteria under Fed. Cir. R. 47.5(a)?</li> <li>✓ Yes (file separate notice; see below)</li> <li>✓ No</li> <li>✓ N/A (amicus/movant)</li> <li>If yes, concurrently file a separate Notice of Related Case Information that complies with Fed. Cir. R. 47.5(b). Please do not duplicate information. This separate</li> </ul> |                                       |                                   |  |

| Notice must only be filed with the first Certificate of Interest or, subsequently, if information changes during the pendency of the appeal. Fed. Cir. R. 47.5(b).                                                                                                                                                                                                                                                                                     |                                       |                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |                                   |  |

| <b>6. Organizational Victims and Bankruptcy Cases</b> . Provide any information required under Fed. R. App. P. 26.1(b) (organizational victims in criminal cases) and 26.1(c) (bankruptcy case debtors and trustees). Fed. Cir. R. 47.4(a)(6).                                                                                                                                                                                                         |                                       |                                   |  |

| ✓ None/Not Applicable                                                                                                                                                                                                                                                                                                                                                                                                                                  | ☐ Additi                              | onal pages attached               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |                                   |  |

FORM 9. Certificate of Interest

Form 9 (p. 1) March 2023

### UNITED STATES COURT OF APPEALS FOR THE FEDERAL CIRCUIT

### **CERTIFICATE OF INTEREST**

Case Number 24-2304

Short Case Caption Netlist, Inc. v. Samsung Electronics Co., Ltd.

$\textbf{Filing Party/Entity} \quad \text{Micron Technology, Inc., Micron Semiconductor Products, Inc., Micron Technology Texas, LLC} \\$

#### **Instructions:**

- 1. Complete each section of the form and select none or N/A if appropriate.

- 2. Please enter only one item per box; attach additional pages as needed, and check the box to indicate such pages are attached.

- 3. In answering Sections 2 and 3, be specific as to which represented entities the answers apply; lack of specificity may result in non-compliance.

- 4. Please do not duplicate entries within Section 5.

- 5. Counsel must file an amended Certificate of Interest within seven days after any information on this form changes. Fed. Cir. R. 47.4(c).

I certify the following information and any attached sheets are accurate and complete to the best of my knowledge.

Date: 09/25/2024 Signature: /s/ E. Joshua Rosenkranz

Name: E. Joshua Rosenkranz

| 1. Represented Entities. Fed. Cir. R. 47.4(a)(1).                                       | 2. Real Party in<br>Interest.<br>Fed. Cir. R. 47.4(a)(2).                                                                                   | 3. Parent Corporations<br>and Stockholders.<br>Fed. Cir. R. 47.4(a)(3).                                                                        |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Provide the full names of all entities represented by undersigned counsel in this case. | Provide the full names of all real parties in interest for the entities. Do not list the real parties if they are the same as the entities. | Provide the full names of all parent corporations for the entities and all publicly held companies that own 10% or more stock in the entities. |

|                                                                                         | ☑ None/Not Applicable                                                                                                                       | ☐ None/Not Applicable                                                                                                                          |

| Micron Technology, Inc.                                                                 |                                                                                                                                             | None                                                                                                                                           |

| Micron Semiconductor Products, Inc.                                                     |                                                                                                                                             | Micron Technology, Inc.                                                                                                                        |

| Micron Technology Texas, LLC                                                            |                                                                                                                                             | Micron Technology, Inc.                                                                                                                        |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

Additional pages attached

| <b>4. Legal Representatives.</b> List all law firms, partners, and associates that (a) appeared for the entities in the originating court or agency or (b) are expected to appear in this court for the entities. Do not include those who have already entered an appearance in this court. Fed. Cir. R. 47.4(a)(4).                                                                                                                                                                                                                                               |                 |                  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|--|--|

| ☐ None/Not Applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ☐ Additiona     | l pages attached |  |  |

| Winston & Strawn LLP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Matthew Hopkins | Ryuk Park        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |                  |  |  |

| 5. Related Cases. Other than the originating case(s) for this case, are there related or prior cases that meet the criteria under Fed. Cir. R. 47.5(a)?  ✓ Yes (file separate notice; see below) ✓ No ✓ N/A (amicus/movant)  If yes, concurrently file a separate Notice of Related Case Information that complies with Fed. Cir. R. 47.5(b). Please do not duplicate information. This separate Notice must only be filed with the first Certificate of Interest or, subsequently, if information changes during the pendency of the appeal. Fed. Cir. R. 47.5(b). |                 |                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |                  |  |  |

| <b>6. Organizational Victims and Bankruptcy Cases</b> . Provide any information required under Fed. R. App. P. 26.1(b) (organizational victims in criminal cases) and 26.1(c) (bankruptcy case debtors and trustees). Fed. Cir. R. 47.4(a)(6).                                                                                                                                                                                                                                                                                                                      |                 |                  |  |  |

| ✓ None/Not Applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ☐ Additiona     | l pages attached |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |                  |  |  |

### TABLE OF CONTENTS

| STATEME | NT OF THE ISSUES                                                                                                                                                                                                      | 1  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| INTRODU | CTION                                                                                                                                                                                                                 | 1  |

| STATEME | NT OF THE CASE                                                                                                                                                                                                        | 4  |

| I.      | There was a known motivation to replace one high-density memory device with multiple (cheaper) low-density memory devices, resulting in similar patent applications by Amidi, Ellsberry, and Netlist                  | 4  |

| II.     | The "chip-select" (CS) signal is used to select a "rank" of one or more memory chips                                                                                                                                  | 5  |

| III.    | Ellsberry used the term "bank" to describe a "rank"                                                                                                                                                                   | 7  |

| IV.     | Amidi and Ellsberry taught "rank multiplication" to double the number of chip-select signals on the module, so that two (cheaper) low-density memory devices could replace one (expensive) high-density memory device | 10 |

| V.      | Netlist's '912 patent, filed after Amidi and Ellsberry, also disclosed "rank multiplication"                                                                                                                          | 11 |

| VI.     | Reexamination of the '912 patent by third parties                                                                                                                                                                     | 14 |

| VII.    | Present IPR proceedings initiated by Samsung and Micron                                                                                                                                                               | 16 |

|         | A. Level of ordinary skill in the art                                                                                                                                                                                 | 18 |

|         | B. The Board properly construed "rank" to include one or more memory devices                                                                                                                                          | 19 |

|         | C. The Board found Ellsberry discloses a single-device rank, rendering claim 16 obvious                                                                                                                               | 20 |

|         | D. The Board found no written-description support for claim 16 in the earlier '436 patent or '244 provisional (filed before Ellsberry)                                                                                | 21 |

| SUMMAR  | Y OF ARGUMENT                                                                                                                                                                                                         | 22 |

| ARGUME  | NT                                                                                                                                                                                                                    | 25 |

| I.      | Standard of Review                                                                                                                                                                                                    | 25 |

| II.     | The Board correctly recognized that a "rank" may have only one memory device                                                                                                                                          | 26 |

|         | A.    |         | claim language itself shows that a "rank" may include a single memory device                                                                       | 27 |

|---------|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|         | В.    |         | specification confirms that a "rank" includes odiments with only a single memory device                                                            | 31 |

|         | C.    | Netli   | st misinterprets the reexamination history                                                                                                         | 38 |

|         | D.    |         | EC standards do not require a different construction ank"                                                                                          | 41 |

| III.    |       |         | evidence supports the Board's determination that scloses all limitations of claim 16                                                               | 44 |

|         | A.    | Figur   | re 12 of Ellsberry discloses a single-device rank                                                                                                  | 44 |

|         | B.    |         | IPRs involving Ellsberry's <i>other</i> embodiments are vant                                                                                       | 49 |

| IV.     | Ellsb | erry is | prior art to claim 16                                                                                                                              | 50 |

|         | A.    | Clain   | n 16 is not supported by the '436 patent                                                                                                           | 51 |

|         |       | 1.      | Substantial evidence supports the Board's conclusion that the '436 patent does not disclose a circuit with both a "register" and a "logic element" | 52 |

|         |       | 2.      | Netlist cannot rely on inferences from a POSITA's knowledge to show written description                                                            | 56 |

|         |       | 3.      | Netlist did not attempt to show that every limitation of claim 16 is disclosed by the '436 patent                                                  | 58 |

|         | B.    | Clain   | n 16 is not supported by the '244 provisional                                                                                                      |    |

| V.      |       | st insu | afficiently presented its alternative arguments for                                                                                                |    |

| CONCLUS | SION  | •••••   |                                                                                                                                                    | 67 |

|         |       |         |                                                                                                                                                    |    |

### TABLE OF AUTHORITIES

| Pa                                                                                                 | age(s) |

|----------------------------------------------------------------------------------------------------|--------|

| Cases                                                                                              |        |

| Alcon Rsch. Ltd. v. Barr Labs., Inc.,<br>745 F.3d 1180 (Fed. Cir. 2014)                            | 57     |

| Almirall, LLC v. Amneal Pharms. LLC,<br>28 F.4th 265 (Fed. Cir. 2022)                              | 25     |

| Ariad Pharms., Inc. v. Eli Lilly & Co., 598 F.3d 1336 (Fed. Cir. 2010) (en banc)                   | 57, 66 |

| Arthrex, Inc. v. Smith & Nephew, Inc., 935 F.3d 1319 (Fed. Cir. 2019)                              | 54     |

| Avid Tech., Inc. v. Harmonic, Inc.,<br>812 F.3d 1040 (Fed. Cir. 2016)                              | 38     |

| Becton, Dickinson & Co. v. Tyco Healthcare Grp., LP,<br>616 F.3d 1249 (Fed. Cir. 2010)             | 55     |

| Callicrate v. Wadsworth Mfg., Inc., 427 F.3d 1361 (Fed. Cir. 2005)                                 | 29     |

| Consol. Edison Co. v. NLRB,<br>305 U.S. 197 (1938)                                                 | 25     |

| Consolo v. Fed. Mar. Comm'n,<br>383 U.S. 607 (1966)                                                | 25, 48 |

| Cont'l Auto. Sys., Inc. v. Intell. Ventures II LLC,<br>IPR2022-00972, Paper 49 (PTAB Dec. 5, 2023) | 60     |

| Dynamic Drinkware, LLC v. Nat'l Graphics, Inc.,<br>800 F.3d 1375 (Fed. Cir. 2015)59, 6             | 50, 61 |

| Epos Techs. Ltd. v. Pegasus Techs. Ltd., 766 F.3d 1338 (Fed. Cir. 2014)                            | 36     |

| Fitbit, Inc. v. BodyMedia, Inc., IPR2016-00707, Paper 9 (PTAB Sept. 8, 2016)                       | 62     |

| Gen. Hosp. Corp. v. Sienna Biopharms., Inc., 888 F.3d 1368 (Fed. Cir. 2018)                                                                                                   | 26 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Genentech, Inc. v. Hospira, Inc.,<br>946 F.3d 1333 (Fed. Cir. 2020)                                                                                                           | 26 |

| Graham v. John Deere Co.,<br>383 U.S. 1 (1966)                                                                                                                                | 25 |

| Hologic, Inc. v. Smith & Nephew, Inc.,<br>884 F.3d 1357 (Fed. Cir. 2018)                                                                                                      | 57 |

| Howmedica Osteonics Corp. v. Wright Med. Tech., Inc., 540 F.3d 1337 (Fed. Cir. 2008)                                                                                          | 37 |

| HTC Corp. v. Cellular Commc'ns Equip., LLC,<br>877 F.3d 1361 (Fed. Cir. 2017)                                                                                                 | 26 |

| Hybritech Inc. v Monoclonal Antibodies, Inc.,<br>802 F.2d 1367 (Fed. Cir. 1986)                                                                                               | 57 |

| Impact Engine, Inc. v. Google LLC,<br>No. 2022-2291, 2024 WL 3287126 (Fed. Cir. July 3, 2024) (nonprecedentia<br>cert. denied, No. 24-836, 2025 WL 663721 (U.S. Mar. 3, 2025) |    |

| In re Gartside,<br>203 F.3d 1305 (Fed. Cir. 2000)                                                                                                                             | 25 |

| Incept LLC v. Palette Life Scis., Inc., 77 F.4th 1366 (Fed. Cir. 2023)                                                                                                        | 48 |

| Intel Corp. v. Qualcomm Inc., 21 F.4th 801 (Fed. Cir. 2021)                                                                                                                   | 29 |

| Jicarilla Apache Nation v. U.S. Dep't of Interior,<br>613 F.3d 1112 (D.C. Cir. 2010)                                                                                          | 60 |

| Kaufman v. Microsoft Corp.,<br>34 F.4th 1360 (Fed. Cir. 2022)                                                                                                                 | 36 |

| Knowles Elecs. LLC v. Cirrus Logic, Inc., 883 F.3d 1358 (Fed. Cir. 2018)                                                                                                      | 56 |

| 550 U.S. 398 (2007)                                                                                                               | 25     |

|-----------------------------------------------------------------------------------------------------------------------------------|--------|

| L.A. Biomedical Rsch. Inst. at Harbor-UCLA Med. Ctr. v. Eli Lilly & Co., 849 F.3d 1049 (Fed. Cir. 2017)                           | 65     |

| Liebel-Flarsheim Co. v. Medrad, Inc., 358 F.3d 898 (Fed. Cir. 2004)                                                               | 29     |

| Linear Tech. Corp. v. ITC,<br>566 F.3d 1049 (Fed. Cir. 2009)                                                                      | 56     |

| Lumi Legend Corp. v. Manehu Prod. All., LLC,<br>PGR2024-00014, 2024 WL 3656822 (PTAB Aug. 5, 2024)                                | 62     |

| Luminara Worldwide, LLC v. Liown Elecs. Co.,<br>814 F.3d 1343 (Fed. Cir. 2016)                                                    | 38     |

| Lupin Ltd. v. Pozen, Inc.,<br>IPR2015-01775, Paper 15 (PTAB Mar. 1, 2016)                                                         | 51, 62 |

| Lynk Labs, Inc. v. Samsung Elecs. Co.,<br>125 F.4th 1120 (Fed. Cir. 2025),<br>reh'g denied, No. 23-2346 (Fed. Cir. Apr. 15, 2025) | 67     |

| Maquet Cardiovascular LLC v. Abiomed Inc.,<br>131 F.4th 1330 (Fed. Cir. 2025)                                                     | 38     |

| Mass. Inst. of Tech. v. Shire Pharms., Inc.,<br>839 F.3d 1111 (Fed. Cir. 2016)                                                    | 38     |

| MaxLite, Inc. v. Jiaxing Super Lighting Elec. Appliance Co., IPR2020-00208, 2021 WL 2221251 (PTAB June 1, 2021)                   | 61     |

| Medtronic, Inc. v. Teleflex Innovations, S.à.r.l.,<br>69 F.4th 1341 (Fed. Cir. 2023)                                              | 48     |

| Mission Integrated Techs., LLC v. Clemente, IPR2023-01285, 2024 WL 752892 (PTAB Feb. 23, 2024)                                    | 62     |

| Nalpropion Pharms., Inc. v. Actavis Labs. FL, Inc.,<br>934 F.3d 1344 (Fed. Cir. 2019)                                             | 57     |

| Nike, Inc. v. Adidas AG,<br>No. 21-1903, 2022 WL 4002668 (Fed. Cir. Sept. 1, 2022) (nonpre | ecedential)54  |

|--------------------------------------------------------------------------------------------|----------------|

| Omega Eng'g, Inc. v. Raytek Corp.,<br>334 F.3d 1314 (Fed. Cir. 2003)                       | 31             |

| Parus Holdings, Inc. v. Google LLC,<br>70 F.4th 1365 (Fed. Cir. 2023)                      | 26, 49, 59, 60 |

| Phillips v. AWH Corp.,<br>415 F.3d 1303 (Fed. Cir. 2005) (en banc)                         | 27, 28, 29     |

| Powell v. Home Depot U.S.A., Inc.,<br>663 F.3d 1221 (Fed. Cir. 2021)                       | 56             |

| Randall Mfg. v. Rea,<br>733 F.3d 1355 (Fed. Cir. 2013)                                     | 25             |

| Regeneron Pharms., Inc. v. Mylan Pharms. Inc.,<br>130 F.4th 1372 (Fed. Cir. 2025)          | 55             |

| Rivera v. ITC,<br>857 F.3d 1315 (Fed. Cir. 2017)                                           | 58, 65, 66     |

| Samsung Elecs. Co. v. Elm 3DS Innovations, LLC,<br>925 F.3d 1373 (Fed. Cir. 2019)          | 26             |

| Sound View Innovations, LLC v. Hulu, LLC, 33 F.4th 1326 (Fed. Cir. 2022)                   | 28             |

| Tech. Licensing Corp. v. Videotek, Inc., 545 F.3d 1316 (Fed. Cir. 2008)                    |                |

| Thryv Inc. v. Click-to-Call Techs. LP,<br>590 U.S. 45 (2020)                               | 67             |

| <i>Trading Techs. Int'l, Inc. v. IBG LLC</i> , 921 F.3d 1378 (Fed. Cir. 2019)              | 67             |

| Wasica Fin. GmbH v. Cont'l Auto. Sys., Inc.,<br>853 F.3d 1272 (Fed. Cir. 2017)             | 30             |

| Wellman, Inc. v. Eastman Chem. Co.,<br>642 F.3d 1355 (Fed. Cir. 2011) | 65, 66 |

|-----------------------------------------------------------------------|--------|

| Wi-LAN, Inc. v. Apple Inc.,<br>811 F.3d 455 (Fed. Cir. 2016)          | 28     |

| <u>Statutes</u>                                                       |        |

| 35 U.S.C. § 103                                                       | 25     |

| Regulations                                                           |        |

| 37 C.F.R. § 42.100(b)                                                 | 20     |

### **STATEMENT OF RELATED CASES**

No appeal in or from the same action was previously before this or any other appellate court. Below are cases known to counsel to be pending in any tribunal that will directly affect or be directly affected by this Court's decision in the pending appeal:

- 1. Netlist, Inc. v. Samsung Electronics Co., Ltd. et al., No. 25-1286 (Fed. Cir.) (appeal of IPR2023-00455 and IPR2023-01142 (PTAB))

- 2. Netlist, Inc. v. Samsung Electronics Co., Ltd. et al., No. 25-1296 (Fed. Cir.) (appeal of IPR2023-00454 and IPR2023-01141 (PTAB))

- 3. Netlist, Inc. v. Samsung Electronics Co., Ltd., No. 2:22-cv-00293 (E.D. Tex.)

- 4. *Netlist, Inc. v. Micron Technology, Inc. et al.*, No. 2:22-cv-00294 (E.D. Tex.)

- 5. *Netlist, Inc. v. Google LLC*, No. 3:09-cv-05718 (N.D. Cal.)

- 6. Samsung Electronics Co., Ltd. et al. v. Netlist, Inc., No 1:21-cv-01453 (D. Del.)

- 7. Netlist, Inc. v. Samsung Electronics Co., Ltd., No. 8:20-cv-00993 (C.D. Cal.)

On January 21, 2025, this Court ordered that this appeal and the following related appeals be treated as companion cases and assigned to the same merits panel: Nos. 25-1286 and 25-1296 (above). *See* ECF No. 22.

### **STATEMENT OF THE ISSUES**

- 1. Whether the Board correctly construed "rank" in claim 16 to cover one or more memory devices, rejecting Netlist's "two or more" proposal, where

- claim 16 does not specify the number of memory devices in a rank, and the Board identified several one-device-per-rank embodiments;

- claim 16 only uses "plurality of" to introduce a different limitation; and

- the previous reexamination did not construe "rank" and merely distinguished prior art teaching "a plurality of memory devices in a rank."

- 2. Whether the Board had substantial evidence to determine that Ellsberry teaches single-device ranks.

- 3. Whether the Board had substantial evidence to determine that neither of the applications Netlist identified as the basis for earlier priority had written description support for claim 16.

### <u>INTRODUCTION</u>

The Board's determination that claim 16 of the '912 patent is unpatentable for obviousness was the product of a thorough analysis, which cannot be dismissed as Petitioner's lucky draw. The Board carefully considered the patent, the prior art,

and the earlier reexamination proceeding to reach a reasoned, fully explained decision entirely consistent with prior rulings.

The sole legal issue Netlist raises is a challenge to the Board's construction of "rank" as encompassing one or more memory devices. Netlist insists a "rank" must have two or more memory devices. But the claim language broadly recites, without restriction, a first or second "number of DDR memory devices" in a rank. The written description is similarly unconstrained and actually discloses single-device ranks. By contrast, the use of "plurality of" for another limitation of claim 16 shows that Netlist claimed a "plurality" when it wanted to do so. The decision not to do so for devices in a rank strongly supports the Board's construction.

Netlist's principal contention is that it disclaimed single-device ranks from claim 16 during reexamination because, Netlist says, the Board adopted that narrower construction and Netlist acquiesced. But the Board correctly determined that it never construed "rank" during reexamination; it merely found that the Amidi prior-art reference—which discloses multiple memory devices in a rank—did not disclose all limitations in claim 16. The Board's acknowledgement of Amidi's multiple-device ranks during reexamination is consistent with the Board's construction here allowing ranks to have one or more memory devices. The reexamination does not support Netlist.

Separate from its claim construction challenge, Netlist seeks reassessment of amply supported facts. First, as to whether Ellsberry teaches claim 16 by disclosing single-device ranks, Netlist comes nowhere close to overcoming substantialevidence review, given that Ellsberry expressly discusses and illustrates a memory module containing single-device ranks. It is irrelevant that a previous Board decision concerning a different patent found that Ellsberry also discloses a different embodiment with multi-device ranks. Second, Netlist asserts that the Court must adopt Netlist's view of how the written description of its earlier applications should be supplemented by various "understandings" to achieve an earlier priority date for the '912 patent. However, the Board's decision rejecting an earlier priority date reasonably found that claim 16's limitations were not described in the earlier applications. For example, the earlier '436 patent application and '244 provisional conspicuously omit the claimed "register" and "bank address signals," respectively, in stark contrast to their express disclosure in the later '912 patent application. There is no basis to reweigh those factual findings on appeal.

Netlist chalks up its loss to a game of chance, but in fact, the Board's decision rests on solid reasoning and evidence. This Court should affirm.

### **STATEMENT OF THE CASE**

I. There was a known motivation to replace one high-density memory device with multiple (cheaper) low-density memory devices, resulting in similar patent applications by Amidi, Ellsberry, and Netlist

The similarity between Netlist's '912 patent and the prior art is no coincidence. In the early 2000s, before the '912 patent was filed, there was a remarkable pricing disparity in the market for memory devices: "[H]igher-density DRAM devices (e.g., 1-Gb DRAM devices) are *much more* than twice the price of lower-density DRAM devices (e.g., 512-Mb DRAM devices)." Appx82 (4:59-62). This created an obvious "economic incentive for utilizing pairs of the lower-density DRAM devices to replace individual higher-density DRAM devices." Appx83 (5:3-5).

Many people recognized this motivation to replace one expensive memory device with two cheaper memory devices, including inventors named Amidi and Ellsberry, which explains the close similarity between the prior art and Netlist's later '912 patent. Appx13229-30. Amidi applied for a patent on January 5, 2004, before Netlist. Appx11867. Amidi recognized, before Netlist, that "[b]ecause memory devices with lower densities are cheaper and more readily available, it may be advantageous to build the above same density memory module using lower densities devices." Appx11878 ¶ [0008]. Ellsberry also recognized, before Netlist filed the

<sup>&</sup>lt;sup>1</sup> All emphasis added unless otherwise noted.

application for the '912 patent, the benefit of "making two smaller-capacity memory devices emulate a single higher-capacity memory device." Appx11884 (Abstract).

# II. The "chip-select" (CS) signal is used to select a "rank" of one or more memory chips

Both Amidi and Ellsberry taught that when replacing one high-density memory device with two low-density memory devices, the two low-density memory devices should receive *different* chip-select signals (often abbreviated "CS"). *See*, *e.g.*, Appx11870 ("cs0" and "cs2"); Appx11901 ("CS0A" and "CS0B").

The chip-select signal is related to the concept of a "rank," and is sometimes called a "rank-select signal[]," as recognized by the '912 patent. Appx81 (2:37-39) ("rank-select signals, also called chip-select signals"); *see also* Appx11193 ("CS . . . Chip Select . . . provides for external *Rank* selection"). But the chip-select signal is also "part of the command code," Appx11193, meaning that any memory chip performing a "Read" or "Write" command needs to receive a chip-select (CS) signal (in combination with several other signals called RAS, CAS, WE, and CKE):

Table 10 — Command truth table.

| Function                  | CKE               |                  |    |     |     |    | BA0        |         |     |         |        |

|---------------------------|-------------------|------------------|----|-----|-----|----|------------|---------|-----|---------|--------|

|                           | Previous<br>Cycle | Current<br>Cycle | cs | RAS | CAS | WE | BA1<br>BA2 | A15-A11 | A10 | A9 - A0 | Notes  |

| Bank Activate             | Н                 | Н                | L  | L   | Н   | Н  | ВА         | Rov     | 1,2 |         |        |

| Write                     | Н                 | Н                | L  | Н   | L   | L  | ВА         | Column  | L   | Column  | 1,2,3, |

| Write with Auto Precharge | Н                 | Н                | L  | Н   | L   | L  | ВА         | Column  | Н   | Column  | 1,2,3, |

| Read                      | Н                 | Н                | L  | Н   | L   | Н  | ВА         | Column  | L   | Column  | 1,2,3  |

| Device Deselect           | Н                 | Х                | H  | х   | х   | х  | х          | х       | х   | ×       | 1      |

NOTE 1 All DDR2 SDRAM commands are defined by states of CS. RAS, CAS, WE and CKE at the rising edge of the clock.

NOTE 2 Bank addresses BA0, BA1, BA2 (BA) determine which bank is to be operated upon. For (E)MRS BA selects an (Extended) Mode Register.

Appx21148 (annotating Appx11236). As shown above, if the chip-select (CS) signal is Low (L), then a read or write command is performed by that memory device, but if the chip-select (CS) signal is High (H), then that memory device is "Deselect[ed]" and does not perform a read or write command.

In summary, if a given chip-select signal (also called rank-select signal) is connected to only one memory device, then only that device will be selected to perform a read or write command when the signal is Low. That is an example of a "rank" with just one memory device. If a given chip-select signal is connected to *two* memory devices, then both of those devices will be selected to perform the command when the signal is Low. That is an example of a "rank" with two memory devices. And so on. Thus, as explained by the Jacob textbook cited repeatedly by Netlist in its brief, "a *rank* of memory is a 'bank' of one or more DRAM devices

that operate in lockstep in response to a given command. . . . [S]ometimes as few as **one** device per rank." Appx11702-03.

### III. Ellsberry used the term "bank" to describe a "rank"

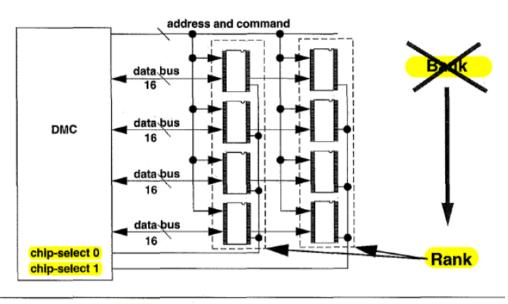

Ellsberry used the term "bank" to describe a "rank," consistent with the common usage of "bank" at the time. See, e.g., Appx11908 ¶ [0055] ("two memory banks 1206 & 1208"). But "bank" was also sometimes used in the industry to refer to other things (such as internal parts of a memory chip) that are not a "rank." See, e.g., Appx13076-78 ¶ 76. So, as explained by the Jacob textbook, the industry started using the term "rank" to "lessen the confusion associated with overloading" the term "bank." Appx11702. That is why the Jacob textbook states that "a rank of memory is a 'bank' of one or more DRAM devices that operate in lockstep in response to a given command." Id. The Jacob textbook provides the following illustration, where the term "bank" in the upper right is crossed out and replaced with the term "rank" to identify the memory devices connected to a given chip-select signal:

FIGURE 10.5: Memory system with 2 ranks of DRAM devices.

Appx11702 (yellow highlighting added). Professor Jacob also published a paper in 2002 that used the term "rank" rather than "bank." Appx11810-12, Appx11817.

This shift in terminology eventually made its way to JEDEC, the industry consortium. For example, the JEDEC standard for DDR SDRAM memory devices first published in 2000 used the term "bank." *See* Appx11271, Appx20270 ("Chip Select... provides for external *bank* selection"). But with the release of the second generation of that standard in 2003, JEDEC adopted the term "rank" to mean the same thing, consistent with Professor Jacob's explanation above. *See* Appx11193 ("Chip Select... provides for external *Rank* selection").

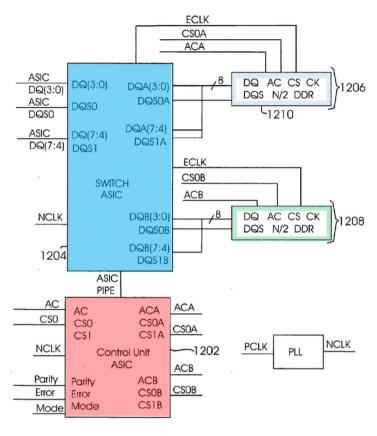

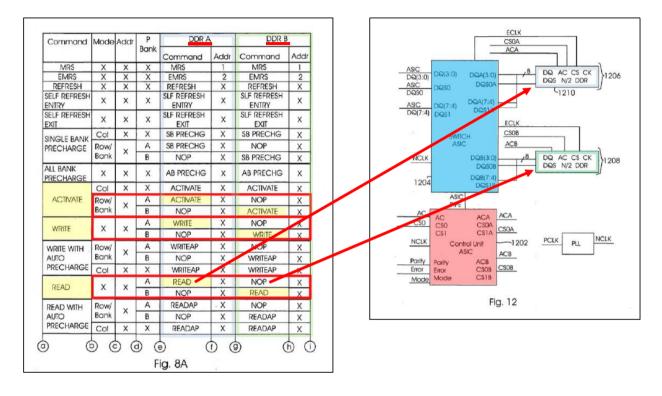

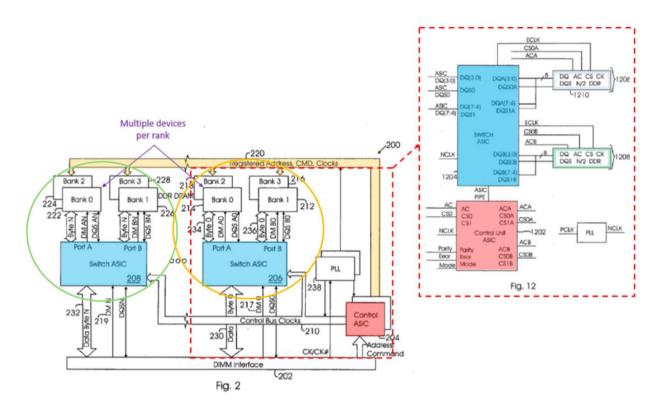

It is undisputed that Ellsberry discloses "ranks" (called "banks" by Ellsberry). Appx38-39; Appx11908 ¶ [0055]. In particular, Figure 12 of Ellsberry, shown below, illustrates a rank (1206, identified by the chip-select signal CS0A) with just

**one** memory device (light blue), and a second rank (1208, identified by the chipselect signals CS0B) with just **one** memory device (green):

Fig. 12

Appx199 (annotating Appx11901); Appx11908 ¶ [0055]; *see also* Appx13181-85 ¶¶ 214-21. Netlist does not dispute that Ellsberry discloses "ranks," but Netlist contends that there would be *additional* memory devices (not shown above) in each "rank" of Ellsberry. *See, e.g.*, Br.51-52. The Board disagreed with Netlist. Appx45-51.

IV. Amidi and Ellsberry taught "rank multiplication" to double the number of chip-select signals on the module, so that two (cheaper) low-density memory devices could replace one (expensive) high-density memory device

As discussed above, both Amidi and Ellsberry taught replacing one (expensive) high-density memory device with two (cheaper) low-density memory devices. They also taught putting logic on the memory module to replace one chipselect signal from the host computer with two chip-select signals on the module—a technique referred to as "rank multiplication" given the relationship between a chipselect signal and a rank. Appx20022-23 (55:9-56:10).

For example, Figure 12 of Ellsberry, reprinted above, shows one chip-select signal (CS0) from the host computer going into the left side of the red "Control Unit," and two chip-select signals (CS0A and CS0B) coming out of the right side and going to the two ranks of memory devices on the upper right (shown outlined in light blue and green). As explained by Ellsberry, "[t]his effectively expands the number of addressable [r]anks per memory module without the need for additional chip select lines on the main memory bus. For example, the invention expands the addressable memory [r]anks on a module by making two smaller-capacity memory devices emulate a single higher-capacity memory device," while still being "compatible with existing system architectures and transparent to the rest of the system." Appx11905 ¶¶ [0026-27]; see also Appx20244; Appx20247; Appx13196-201 ¶¶ 232-36; Appx13203-07 ¶¶ 240-42.

Similarly, Amidi teaches that a "standard" memory module only receives "two chip select signals" from the host computer, Appx11878 ¶¶ [0010-11], but Amidi teaches putting logic on the memory module to double the number of chipselect signals to "four chip select signals (cs0, cs1, cs2, and cs3)," Appx11880 ¶¶ [0036], corresponding to four ranks of memory devices, Appx11879-80 ¶¶ [0034-35]; Appx11870.

Although Ellsberry and Amidi share many similarities, one difference is that Ellsberry discloses an example of a single-device rank, as discussed above, while Amidi only discloses examples of "ranks" with *multiple* memory devices in each rank. *See, e.g.*, Appx11870 (chip-select signal "cs0" connected to *both* memory devices "U1" and "U9" in "First Rank"); Appx11879 ¶ [0034] ("first rank 304 of memory devices 306 (U1 through U9)").

## V. Netlist's '912 patent, filed after Amidi and Ellsberry, also disclosed "rank multiplication"

On July 1, 2005—one month after Ellsberry's application and over a year after Amidi's application—Netlist filed an application ultimately leading to the '912 patent. Appx60.

Like Amidi and Ellsberry, the '912 patent teaches replacing one high-density memory device with two cheaper low-density memory devices, Appx83 (5:1-5), and replacing one chip-select signal from the host computer with two chip-select signals on the memory module—which Netlist calls "rank multiplication," Br.10-11.

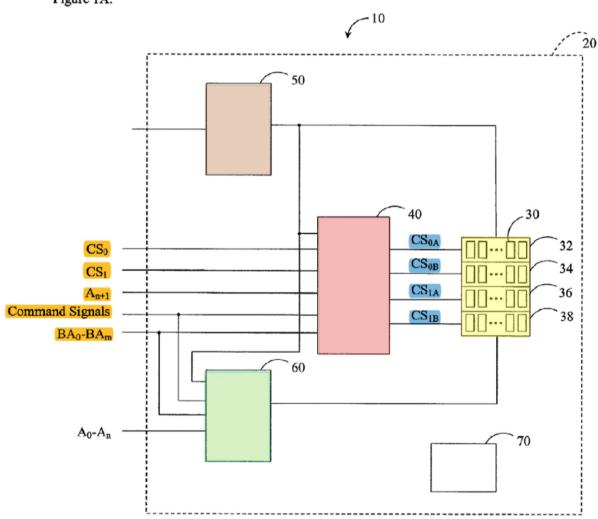

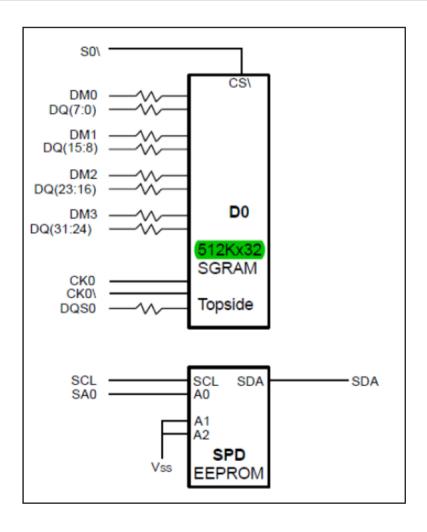

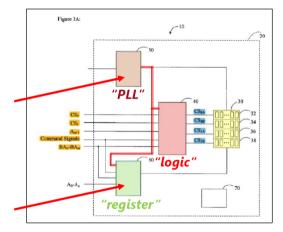

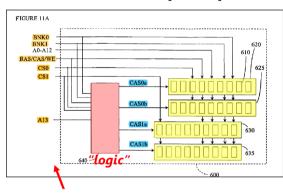

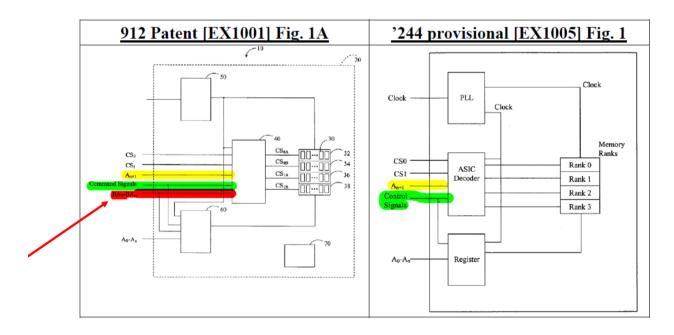

Figure 1A of the '912 patent, shown below, is remarkably similar to Amidi, because it teaches a logic element 40 (red) that receives two chip-select signals from the left (CS<sub>0</sub> and CS<sub>1</sub> in orange)—designed to control *two* ranks of memory devices—and outputs four chip-select signals on the right (CS<sub>0A</sub>, CS<sub>0B</sub>, CS<sub>1A</sub>, CS<sub>1B</sub> in blue)—which control *four* ranks (32, 34, 36, 38), with each rank including multiple memory devices (30, yellow):

Figure 1A: 20 50 40 30  $CS_{0A}$ 32  $CS_{0B}$ 34  $CS_{1A}$  $A_{n+1}$ 36 Command Signals CS<sub>IB</sub> 38 BA<sub>0</sub>-BA<sub>m</sub> 60  $A_0-A_n$ 70

Appx136 (annotating Appx63); Appx84 (7:35-54); Appx7-8. In Figure 1A above, the green box (60) is a "register," and the brown box (50) is a "phase-lock loop" (PLL) device. Appx83 (5:22-25).

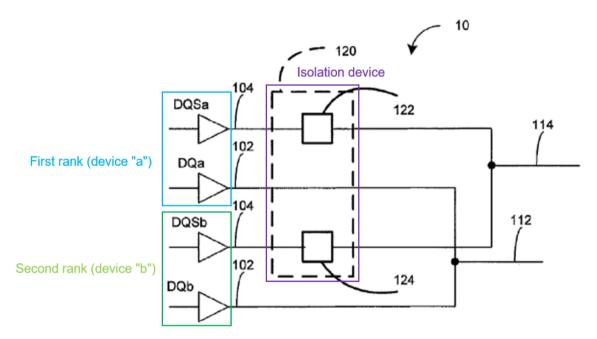

Figure 1A above is an embodiment corresponding to original claim 15 of the '912 patent, which as discussed below was rejected during reexamination in light of Amidi in combination with JEDEC standards. However, Figure 1A above does not disclose claim 16—which originally depended from claim 15 and survived reexamination—because Figure 1A does not disclose the last limitation [16.e] requiring that "the command signal is transmitted to only one DDR memory device at a time." Appx103 (3:42-43). Instead Figure 1A shows the register 60 (green) transmitting the same command and address signals to all of the memory devices 30, and shows the logic element 40 (red) transmitting each chip select signal (e.g., CS<sub>0A</sub>, blue) to all of the memory devices 30 in a given rank (e.g., rank 32, yellow). Appx20139-40 (172:15-173:23). The only disclosed embodiment in the '912 patent that transmits the command signal "to only one DDR memory device at a time," as required by claim 16, is an embodiment with just *one* memory device in each rank (similar to Figure 12 of Ellsberry). See Appx21153; Appx15-18 (discussing Appx84 (8:48-60)); Appx1016, Appx1021 ([16.e]).

### VI. Reexamination of the '912 patent by third parties

After the '912 patent issued in November 2009, Netlist quickly asserted it (but not claim 16) against third parties, including Google. Appx12809 (1:3-23). Those lawsuits resulted in an *inter partes* reexamination of the '912 patent, Appx12811 (3:3-20), including (as relevant to this appeal) claims 15 and 16, Appx10487. Micron and Samsung, the Appellees here, were not involved in that litigation or the resulting reexamination.

In the reexamination, Netlist admitted that "Amidi is probably the closest reference to the claims of the '912 patent," Appx4011, but Ellsberry was never substantively considered, apparently due to the mistaken belief that Ellsberry was not prior art because it was "filed after the ['912 patent] application's earliest effective filing date," Appx2210; Appx470, Appx486-88. As a result, the focus of the reexamination was on Amidi (alone and in combination with other references).

During reexamination, original claim 15 (from which claim 16 originally depended, Appx97) was found obvious over Amidi in view of certain JEDEC standards. Appx5410-14. That rejection resulted in extensive amendments to claim 15 (among other claims). Appx102-03 (2:52-3:8).

However, dependent claim 16—with limitation [16.e] requiring "the command signal is transmitted to *only one* DDR memory device at a time"—was *not* found obvious over Amidi. The Board made factual findings during the

reexamination, shown below, that Amidi (like Figure 1A of the '912 patent discussed above) discloses *multiple* memory devices in each rank, meaning any read or write command would be sent to *all* those memory devices at a time, rather than "only one ... at a time" as required by claim 16. The Board's full discussion includes important text omitted by Netlist (Br.16-17, 21, 32, 34, 37-38):

Requester 1 argues that Amidi teaches the limitation of "the command signal is transmitted to only one DDR memory device at a time." . . . .

We agree that Amidi teaches using a command signal to read or write . . . . Yet, as the Examiner indicates:

Requester 1 asserts that "[o]ne of ordinary skill in the art would have understood from the '152 publication [of Amidi] that the command signal may be transmitted to the DDR memory devices serially in a sequential fashion" without any reasoned explanation to support the assertion. . . . . . The claims require transmission of a command signal to only one DDR memory device at a time. Requester has not provided a reasonable explanation as to why one skilled in the art would transmit a command signal to only one DDR memory device at a time when there is a plurality of memory devices in a rank.

RAN 29 [Appx7494] (emphasis added).

That is, Figures 6A and 6B of Amidi show various command signals (e.g., CS0, CS1, CKE, CAS, RAS, and WE) being transmitted to more than one memory device. Amidi ¶ 62, Fig. 6A-6B (stating "Signals to Memory Devices" at the far right)

Appx10560-61 (emphasis by the Board); Appx11874-75 (Amidi's Figs. 6A and 6B stating "Signals to Memory Devices"); Appx11882 (Amidi ¶ 62).

This Court summarily affirmed, *see Google LLC v. Netlist, Inc.*, 810 F. App'x 902 (Fed. Cir. June 15, 2020), and the reexamination certificate issued in 2021 with claim 16 rewritten in independent form (with no other changes) by adding rejected base claim 15's limitations. Appx101, Appx103 (3:9-43); *see also* Appx6353 (ii); Appx15120 (18:2-8), Appx15130 (28:4-6).

### VII. Present IPR proceedings initiated by Samsung and Micron

Netlist did not suggest that Samsung might be infringing the '912 patent until after the reexaminations concluded in 2021, which motivated Samsung to challenge claim 16<sup>2</sup> in the present IPR for the first time. *See* Appx243-45 (citing Appx12918-19 ¶ 14; Appx12925 ¶ 40; Appx12812 (4:5-11); Appx12817-18 (9:14-10:26)).

Samsung filed an IPR petition challenging claim 16 on three grounds: (1) obviousness over Perego (Appx11831); (2) obviousness over the combination of Perego and Amidi; and (3) obviousness over Ellsberry. Appx132; Appx10-11. The Board later joined Micron<sup>3</sup> to the proceedings. Appx21389-92; Appx884.

Netlist contended that Samsung (but not Micron) should be time-barred from seeking *inter partes* review because of its relationship with Google, whom Netlist

<sup>&</sup>lt;sup>2</sup> All other previously asserted claims of the '912 patent were amended during reexamination and subject to intervening rights, Appx15146 (44:5-10), leaving only claim 16 the subject of the current litigation, Appx15156 (10:4-10), Appx15159 (13:5-15), Appx15163 (17:18-20); Appx15807.

<sup>&</sup>lt;sup>3</sup> "Micron" refers to Micron Technology, Inc., Micron Semiconductor Products, Inc., and Micron Technology Texas LLC. Appx1 n.1.

had sued for infringement in 2009 as discussed above. Appx473. The Board, after permitting discovery on the issue, rejected Netlist's argument. Appx2-3.

In the Petition, Petitioner proposed that the term "rank" should be construed to mean "an independent set of *one or more* memory devices on a memory module that act together in response to command signals, including chip select signals, to read or write the full bit-width of the memory module." Appx140-42; Appx13075-79 ¶¶ 73-77; Appx411-13. Petitioner later proposed the same construction for "rank" in a different IPR involving the related '215 patent. In two institution decisions involving the '912 patent, and a third institution decision involving the related '215 patent, the Board preliminarily construed "rank" to include one or more memory devices, agreeing with Petitioner's proposal and rejecting Netlist's proposal requiring two or more memory devices. Appx490-95 (Oct. 19, 2022); Appx874-76 (June 7, 2023); Appx19941-45 (Aug. 1, 2023). In related litigation, the district court also rejected Netlist's arguments and construed "rank" in the '912 and '215 patents to include "one or more" memory devices. Appx20949-52, Appx20973 (Nov. 21, 2023).

In its final written decision, the Board determined that claim 16 of the '912 was unpatentable over Ellsberry, without reaching Grounds 1 and 2 involving Perego, as discussed below. Appx55.

### A. Level of ordinary skill in the art

With respect to the level of skill in the art, the Board found in the final written decision (and Netlist does not challenge on appeal) that a POSITA "would have been familiar with various standards of the day, including JEDEC industry standards." Appx12-13. Contrary to Netlist's arguments on appeal that JEDEC *required* DDR memory modules to be 64- or 72-bits wide, Br.7-9, 39, the Board found that "JEDEC standards permitted 8-bit and 16-bit wide modules" consistent with Figure 12 of Ellsberry showing an 8-bit-wide memory module with a single x8 (i.e., 8-bit-wide) DDR memory device in each rank. Appx51.

The JEDEC standard cited by the Board, called the "SPD" standard for DRAM modules, Appx20382, is discussed by the '912 patent, Appx85 (9:23-10:55), and consistent with that standard, the '912 patent expressly permits modules *less* than 64-bits wide (contrary to Netlist's argument on appeal, Br.7-9, 39): "[M]emory modules ... having widths of ... 32 bits ... as well as other widths ... are compatible with embodiments described herein." Appx83 (5:60-64). "In addition, memory devices ... having bit widths of 4, 8, 16, 32, as well as other bit widths, are compatible with embodiments described herein." Appx83 (6:16-19). For example, JEDEC had standardized a 32-bit-wide module with a single x32 (i.e., 32-bit-wide) DDR memory device—a rank with only one memory device. Appx21151 (annotating Appx20427, Appx20433).

### B. The Board properly construed "rank" to include one or more memory devices

Both parties agreed before the Board that the "dispositive issue for claim construction" is whether the claimed "*rank*" may include only one memory device or whether it must include at least two memory devices. Appx14.

The Board concluded that "the claim term 'rank' may include only one memory device." Appx14-24. The Board determined that the claim language on its face "does not preclude the possibility that a rank could have a single memory device." Appx14-15. Claim 55's additional requirement that each rank comprises a "plurality" of memory devices, when contrasted with claim 16, "implies that each of the ranks [in claims without that requirement] could include a single memory device." Appx15. The Board also determined that the '912 patent discloses embodiments with single-device ranks. Appx15-23. The Board rejected Netlist's arguments that claim 16 is limited to a memory module "compliant with a JEDEC standard" and in any event made factual findings that JEDEC permitted single-device ranks (e.g., one 8-bit memory device on an 8-bit-wide module). Appx51.