Case No. 23-2007, Case No. 23-2095

# United States Court of Appeals for the Federal Circuit

MICRON TECHNOLOGY, INC., MICRON SEMICONDUCTOR PRODUCTS, INC., MICRON TECHNOLOGY TEXAS, LLC, STATE OF IDAHO, *Plaintiffs-Appellees*

v.

## LONGHORN IP, LLC, Defendant-Appellant

Case No. 23-2007: Appeal from the United States District Court for the District of Idaho in No. 1:22-cv-00273-DCN, Judge David C. Nye.

## KATANA SILICON TECHNOLOGIES LLC, Plaintiff-Appellant

v.

MICRON TECHNOLOGY, INC., MICRON SEMICONDUCTOR PRODUCTS, INC., MICRON TECHNOLOGY TEXAS, LLC, STATE OF IDAHO, Defendants-Appellees

Case No. 23-2095: Appeal from the United States District Court for the District of Idaho in No. 1:22-cv-00282-DCN, Judge David C. Nye.

## CORRECTED OPENING BRIEF OF APPELLANTS KATANA SILICON TECHNOLOGIES LLC AND LONGHORN IP, LLC

SCOTT W. BREEDLOVE JOSHUA BENNETT OMER SALIK CARTER ARNETT PLLC 8150 N. Central Expressway, Suite 500 214-550-8188 Dallas, Texas 75206 Counsel for Appellants

February 22, 2024

## **EXEMPLARY PATENT CLAIMS**

## Claim 1 of RE38,806 patent

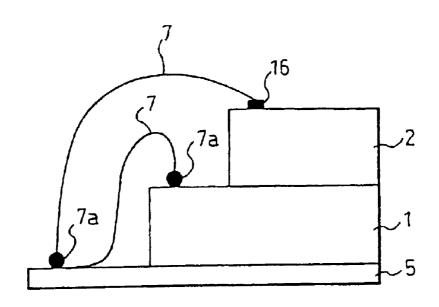

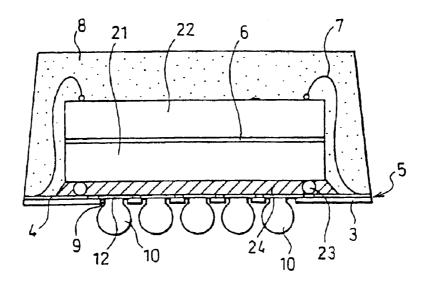

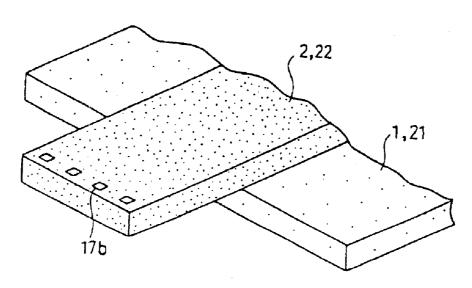

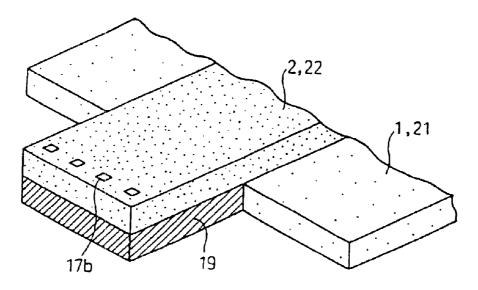

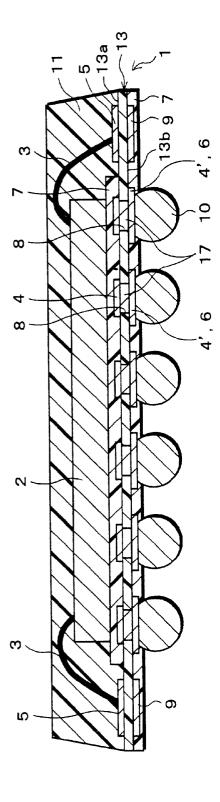

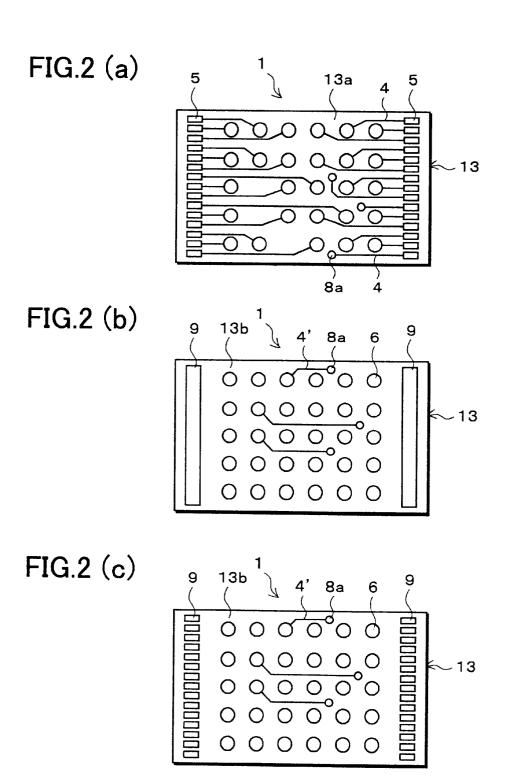

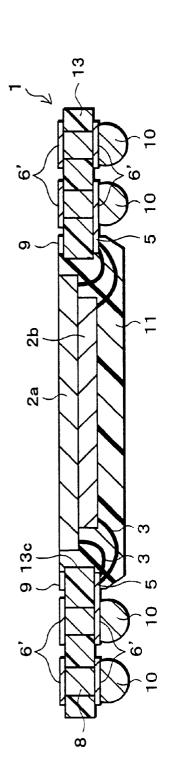

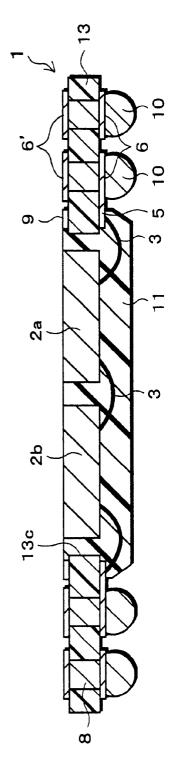

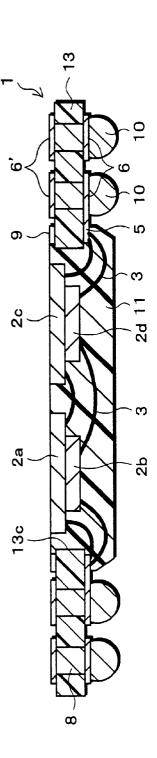

1. A semiconductor device including a stacked package structure and a chip size package structure, comprising:

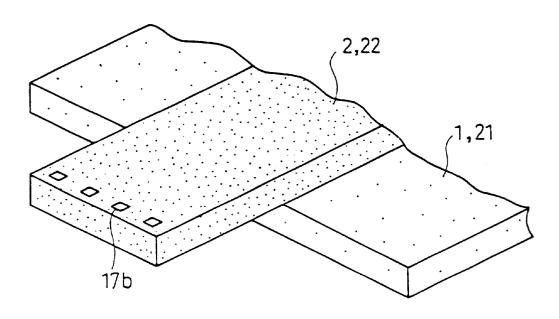

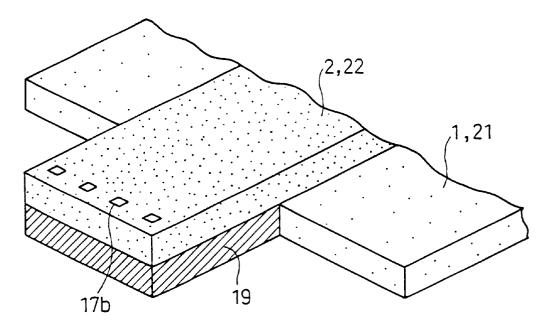

an insulating substrate including a wiring layer having electrode sections; a first semiconductor chip having a first adhesion layer adhered to its back surface where a circuit is not formed, said first semiconductor chip being mounted on said wiring layer through the first insulating adhesion layer; and a second semiconductor chip having a second adhesion layer adhered to its back surface where a circuit is not formed, said second semiconductor chip being mounted on a circuit-formed front surface of said first semiconductor chip through the second insulating adhesion layer;

each of said first and second semiconductor chips being wire-bonded to the electrode section with a wire, said first and second semiconductor chips and the wire being sealed with a resin.

## Claim 1 of 6,352,879 patent

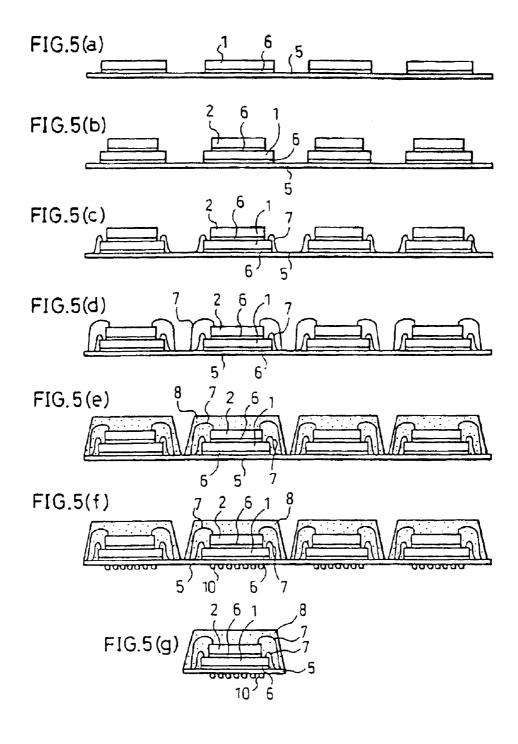

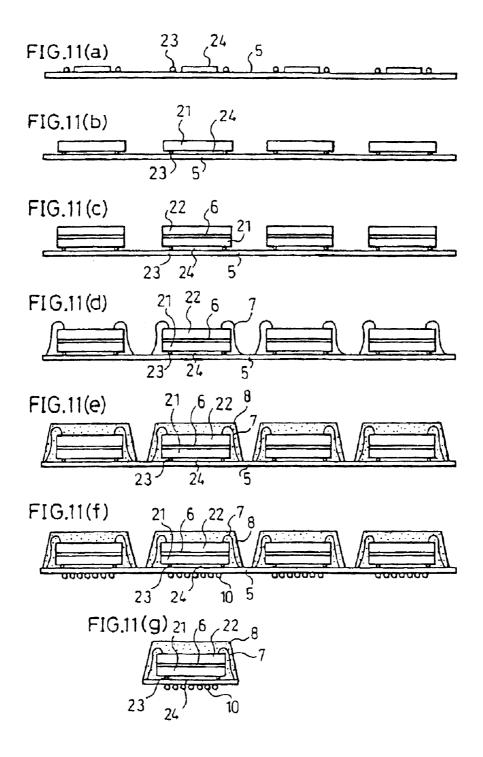

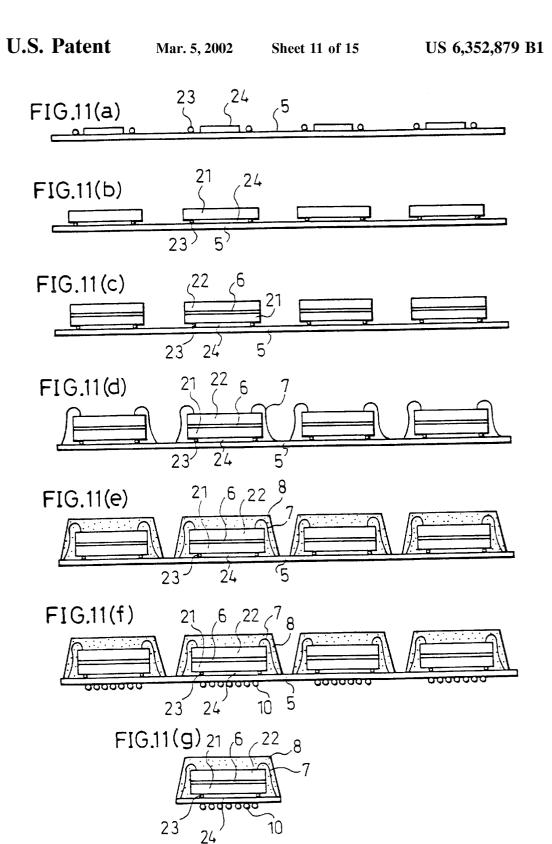

- 1. A method of manufacturing a semiconductor device comprising:

- (a) forming a first adhesion layer on a back surface of a first wafer on which no circuit is formed, a circuit being formed on a front surface of the first wafer;

- (b) producing separate first semiconductor chips from said first wafer by dicing;

- (c) mounting said first semiconductor chip on a wiring layer with its back surface facing said wiring layer;

- (d) forming a second adhesion layer on a back surface of a second wafer on which no circuit is formed, a circuit being formed on a front surface of the first wafer;

- (e) producing separate second semiconductor chips from said second wafer by dicing; and

- (f) mounting said second semiconductor chip on said first semiconductor chip with its back surface facing said first semiconductor chip.

## **Claim 11 of 6,731,013 patent**

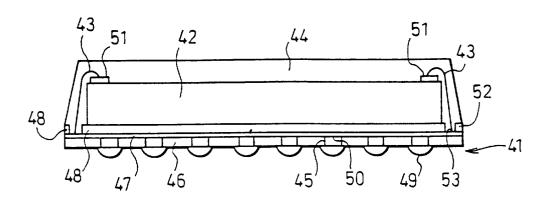

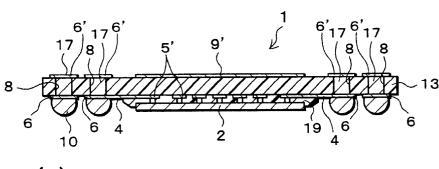

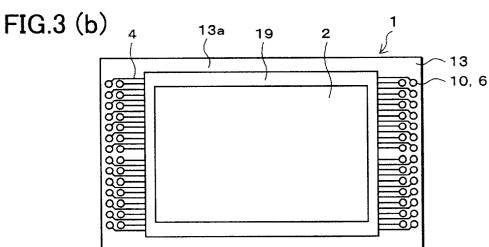

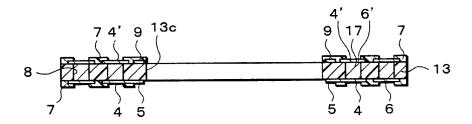

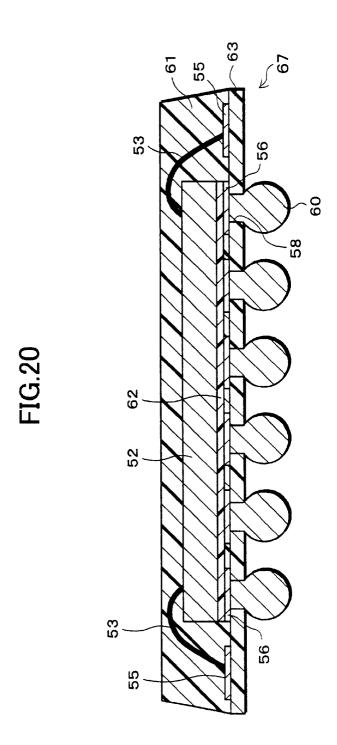

11. A semiconductor device comprising:

an insulating substrate;

a terminal section, provided on a first surface of the insulating substrate, for making connection by wire bonding;

a land section, provided on the insulating substrate, for an external connection terminal;

wiring patterns, respectively provided on the first surface and a second surface on the other side of the first surface, for making electrical connection between the terminal section and the land section;

a support pattern, provided on the second surface corresponding in position to the terminal section, for improving wire bonding connection, wherein the support pattern is not electrically connected to one of the terminal section and land section;

a semiconductor chip mounted on the insulating substrate;

- a bonding wire section for making electrical connection between the terminal section and the semiconductor chip;

- a resin sealing section for sealing a circuit forming surface of the semiconductor chip and the bonding wire section; and

- a conductive member, provided on the land section, for connecting the semiconductor chip to outside.

FORM 9. Certificate of Interest

Form 9 (p. 1) March 2023

## UNITED STATES COURT OF APPEALS FOR THE FEDERAL CIRCUIT

## **CERTIFICATE OF INTEREST**

| Case Number               | 2023-2007                                  |

|---------------------------|--------------------------------------------|

| <b>Short Case Caption</b> | Micron Technology Inc. v. Longhorn IP, LLC |

| Filing Party/Entity       | Longhorn IP, LLC                           |

#### **Instructions:**

- 1. Complete each section of the form and select none or N/A if appropriate.

- 2. Please enter only one item per box; attach additional pages as needed, and check the box to indicate such pages are attached.

- 3. In answering Sections 2 and 3, be specific as to which represented entities the answers apply; lack of specificity may result in non-compliance.

- 4. Please do not duplicate entries within Section 5.

- 5. Counsel must file an amended Certificate of Interest within seven days after any information on this form changes. Fed. Cir. R. 47.4(c).

I certify the following information and any attached sheets are accurate and complete to the best of my knowledge.

| Date: <u>2/22/2024</u> | Signature: | /s/ Scott W. Breedlove |

|------------------------|------------|------------------------|

|                        | Name:      | Scott W. Breedlove     |

|                        |            |                        |

Case: 23-2007 Document: 28 Page: 5 Filed: 02/22/2024

FORM 9. Certificate of Interest

Form 9 (p. 2) March 2023

| 1. Represented Entities. Fed. Cir. R. 47.4(a)(1).                                       | 2. Real Party in<br>Interest.<br>Fed. Cir. R. 47.4(a)(2).                                                                                   | 3. Parent Corporations<br>and Stockholders.<br>Fed. Cir. R. 47.4(a)(3).                                                                        |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Provide the full names of all entities represented by undersigned counsel in this case. | Provide the full names of all real parties in interest for the entities. Do not list the real parties if they are the same as the entities. | Provide the full names of all parent corporations for the entities and all publicly held companies that own 10% or more stock in the entities. |

|                                                                                         | ☑ None/Not Applicable                                                                                                                       | ☐ None/Not Applicable                                                                                                                          |

| Longhorn IP, LLC                                                                        |                                                                                                                                             | Tanit Ventures Inc.                                                                                                                            |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         | Additional pages attach                                                                                                                     | ed                                                                                                                                             |

V

|   |      |    |   | _   |         |       | -    |      |

|---|------|----|---|-----|---------|-------|------|------|

| ı | F(O) | KM | 9 | Cer | tificat | te of | Inte | rest |

Form 9 (p. 3) March 2023

| 4. Legal Representatives. List all law firms, partners, and associates that (a) appeared for the entities in the originating court or agency or (b) are expected to appear in this court for the entities. Do not include those who have already entered an appearance in this court. Fed. Cir. R. 47.4(a)(4).                                                                                                                                                                                                                                                      |                                                   |                                       |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------|--|--|--|

| □ None/Not Applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ☐ Additiona                                       | l pages attached                      |  |  |  |

| Nathan I. Cox, (formerly Carter Arnett<br>PLLC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Daniel L. Schmid (formerly Carter<br>Arnett PLLC) | Keely E. Duke, Duke Evett, PLLC       |  |  |  |

| Seth Lindner (formerly Carter Arnett<br>PLLC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | E. Leon Carter, Carter Arnett PLLC                | Bradley D. Liddle, Carter Arnett PLLC |  |  |  |

| Michael Pomeroy, Carter Arnett PLLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Omer Salik, Carter Arnett PLLC                    | Joshua J. Bennett, Carter Arnett PLLC |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |                                       |  |  |  |

| 5. Related Cases. Other than the originating case(s) for this case, are there related or prior cases that meet the criteria under Fed. Cir. R. 47.5(a)?  ✓ Yes (file separate notice; see below) ✓ No ✓ N/A (amicus/movant)  If yes, concurrently file a separate Notice of Related Case Information that complies with Fed. Cir. R. 47.5(b). Please do not duplicate information. This separate Notice must only be filed with the first Certificate of Interest or, subsequently, if information changes during the pendency of the appeal. Fed. Cir. R. 47.5(b). |                                                   |                                       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |                                       |  |  |  |

| 6. Organizational Victims and Bankruptcy Cases. Provide any information required under Fed. R. App. P. 26.1(b) (organizational victims in criminal cases) and 26.1(c) (bankruptcy case debtors and trustees). Fed. Cir. R. 47.4(a)(6).  None/Not Applicable  Additional pages attached                                                                                                                                                                                                                                                                              |                                                   |                                       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |                                       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |                                       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |                                       |  |  |  |

FORM 9. Certificate of Interest

Form 9 (p. 1) March 2023

## UNITED STATES COURT OF APPEALS FOR THE FEDERAL CIRCUIT

## **CERTIFICATE OF INTEREST**

Case Number 2023-2095

Short Case Caption Katana Silicon Technologies LLC v. Micron Technology Inc

$\textbf{Filing Party/Entity} \hspace{0.2cm} \textbf{Katana Silicon Technologies LLC}$

#### **Instructions:**

- 1. Complete each section of the form and select none or N/A if appropriate.

- 2. Please enter only one item per box; attach additional pages as needed, and check the box to indicate such pages are attached.

- 3. In answering Sections 2 and 3, be specific as to which represented entities the answers apply; lack of specificity may result in non-compliance.

- 4. Please do not duplicate entries within Section 5.

- 5. Counsel must file an amended Certificate of Interest within seven days after any information on this form changes. Fed. Cir. R. 47.4(c).

I certify the following information and any attached sheets are accurate and complete to the best of my knowledge.

| Date: <u>2/22/2024</u> | Signature: | /s/ Scott W. Breedlove |

|------------------------|------------|------------------------|

|                        | _          |                        |

|                        | Name:      | Scott W. Breedlove     |

FORM 9. Certificate of Interest

Form 9 (p. 2) March 2023

| 1. Represented Entities. Fed. Cir. R. 47.4(a)(1).                                       | 2. Real Party in<br>Interest.<br>Fed. Cir. R. 47.4(a)(2).                                                                                   | 3. Parent Corporations<br>and Stockholders.<br>Fed. Cir. R. 47.4(a)(3).                                                                        |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Provide the full names of all entities represented by undersigned counsel in this case. | Provide the full names of all real parties in interest for the entities. Do not list the real parties if they are the same as the entities. | Provide the full names of all parent corporations for the entities and all publicly held companies that own 10% or more stock in the entities. |

|                                                                                         | ☑ None/Not Applicable                                                                                                                       | ☐ None/Not Applicable                                                                                                                          |

| Katana Silicon Technologies LLC                                                         |                                                                                                                                             | Tanit Ventures Inc.                                                                                                                            |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         |                                                                                                                                             |                                                                                                                                                |

|                                                                                         | Additional pages attach                                                                                                                     | ed                                                                                                                                             |

viii

| FORM ! | 9. | Certificate | of | Interest |

|--------|----|-------------|----|----------|

|--------|----|-------------|----|----------|

Form 9 (p. 3) March 2023

| 4. Legal Representatives. List all law firms, partners, and associates that (a) appeared for the entities in the originating court or agency or (b) are expected to appear in this court for the entities. Do not include those who have already entered an appearance in this court. Fed. Cir. R. 47.4(a)(4).                                                                                                                                                                                                                                                 |                                                   |                                       |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------|--|--|--|

| □ None/Not Applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ☐ Additiona                                       | l pages attached                      |  |  |  |

| Nathan I. Cox, (formerly Carter Arnett<br>PLLC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Daniel L. Schmid (formerly Carter<br>Arnett PLLC) | Keely E. Duke, Duke Evett, PLLC       |  |  |  |

| Seth Lindner (formerly Carter Arnett PLLC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | E. Leon Carter, Carter Arnett PLLC                | Bradley D. Liddle, Carter Arnett PLLC |  |  |  |

| Michael Pomeroy, Carter Arnett PLLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Omer Salik, Carter ArnettPLLC                     | Joshua J. Bennett, Carter Arnett PLLC |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                   |                                       |  |  |  |

| 5. Related Cases. Other than the originating case(s) for this case, are there related or prior cases that meet the criteria under Fed. Cir. R. 47.5(a)?  Yes (file separate notice; see below)  No N/A (amicus/movant)  If yes, concurrently file a separate Notice of Related Case Information that complies with Fed. Cir. R. 47.5(b). Please do not duplicate information. This separate Notice must only be filed with the first Certificate of Interest or, subsequently, if information changes during the pendency of the appeal. Fed. Cir. R. 47.5(b). |                                                   |                                       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                   |                                       |  |  |  |

| 6. Organizational Victims and Bankruptcy Cases. Provide any information required under Fed. R. App. P. 26.1(b) (organizational victims in criminal cases) and 26.1(c) (bankruptcy case debtors and trustees). Fed. Cir. R. 47.4(a)(6).                                                                                                                                                                                                                                                                                                                         |                                                   |                                       |  |  |  |

| ✓ None/Not Applicable ☐ Additional pages attached                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                   |                                       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                   |                                       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                   |                                       |  |  |  |

## TABLE OF CONTENTS

| TABLE | OF AUTHORITIESxiii                                                                                                                                         |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TABLE | OF ABBREVIATIONS AND CONVENTIONS xix                                                                                                                       |

| I.    | INTRODUCTION                                                                                                                                               |

| II.   | STATEMENT OF RELATED CASES                                                                                                                                 |

| III.  | JURISDICTIONAL STATEMENT                                                                                                                                   |

|       | A. Interlocutory Appeal                                                                                                                                    |

|       | 1. This Court Has Jurisdiction Under Section 1292(a)(1) & (c)(1)                                                                                           |

|       | a. The Order Is Injunctive5                                                                                                                                |

|       | b. The Injunction and Bond Are Punitive and Chilling in Their Effect, Requiring Immediate Appeal                                                           |

|       | 2. This Court Also Has Jurisdiction Under the Collateral Order Doctrine Applied to Bonds, as in <i>Cohen</i>                                               |

|       | 3. The Court May Also Exercise Pendent Jurisdiction                                                                                                        |

|       | B. Alternative Relief Under 28 U.S.C. § 1651                                                                                                               |

| IV.   | STATEMENT OF THE ISSUES                                                                                                                                    |

| V.    | STATEMENT OF THE CASE                                                                                                                                      |

|       | A. Katana Identified Micron as an Infringer in 2018 and Initiated License Negotiations                                                                     |

|       | B. Katana Sued Micron for Patent Infringement in 2022, and Micron Then Sued Longhorn in Idaho State Court in Retaliation, Relying on the Idaho BFA Statute |

|      | The Idaho BFA Statute Regulates Federal Patent     Litigation                                                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 2. The District Court Allowed Longhorn No Discovery in Response to Micron's State-Law Motion for a \$15 Million Bond.                                                                           |

|      | C. In Addition to Denying Appellants' Motions to Dismiss, the District Court Also Ordered the \$8-Million Bond Based Solely on Micron's Pleadings, Assumed (Wrongly) To Be True.                |

| VI.  | SUMMARY OF THE ARGUMENT                                                                                                                                                                         |

| VII. | ARGUMENT                                                                                                                                                                                        |

|      | A. Standard of Review                                                                                                                                                                           |

|      | B. The District Court Erred in Entering the Order                                                                                                                                               |

|      | Micron's BFA Claim Is Preempted for Failing to State a     Plausible Claim of Objective Baselessness                                                                                            |

|      | <ol> <li>Idaho's Act Is Facially Preempted Because It Would Displace<br/>Congress's Chosen Calculus of Patent Litigation Incentives<br/>and Lead to Stark Nationwide Non-Uniformity.</li> </ol> |

|      | C. The District Court Abused Its Discretion by Applying State Law to Order a Punitive, Coercive Bond as a Precondition to Katana Enforcing Its Patents in Federal Court.                        |

|      | The district court applied the Act's bond provision wrongly and unconstitutionally.                                                                                                             |

|      | 2. The bond is unconstitutional for the additional reason that the Act is preempted as applied to Micron's theory of the case                                                                   |

|      | D. Absent Appellate Relief, the Court Should Order Mandamus Relief Because the Bond Precondition Was Clearly Erroneous and No Other Relief Would Be Adequate                                    |

| VIII. | CONCLUSION | 53 |

|-------|------------|----|

| ADD]  | ENDUM      | 55 |

## TABLE OF AUTHORITIES

| Cases                                                    |

|----------------------------------------------------------|

| 800 Adept, Inc. v. Murex Secs., Ltd.,                    |

| 539 F.3d 1354 (Fed. Cir. 2008)34                         |

| Abbas v. Foreign Pol'y Grp., LLC,                        |

| 783 F.3d 1328 (D.C. Cir. 2015)                           |

| 783 F.3d 1328 (D.C. Cli. 2013)43, 32                     |

| Abbott v. Perez,                                         |

| 138 S. Ct. 2305 (2018)                                   |

| Azizian v. Federated Dep't Stores, Inc.,                 |

| 499 F.3d 950 (9th Cir. 2007)                             |

| 47) 1.3d 730 (7th Ch. 2007)0, 40                         |

| Bldg. Innovation Indus., L.L.C. v. Onken,                |

| 473 F. Supp. 2d 978 (D. Ariz. 2007)43                    |

| Boggs v. Boggs,                                          |

| 520 U.S. 833 (1997)                                      |

| 320 0.5. 033 (1777)                                      |

| Buchanan v. Sullivan,                                    |

| No. 8:20-CV-301, 2021 WL 149052 (D. Neb. Jan. 15, 2021)6 |

| Burgert v. Lokelani Bernice Pauahi Bishop Tr.,           |

| 200 F.3d 661 (9th Cir. 2000)                             |

| 200 1 .3d 001 (3th Ch. 2000)                             |

| C.R. Bard, Inc. v. M3 Sys., Inc.,                        |

| 157 F.3d 1340 (Fed. Cir. 1998)passim                     |

| Carson v. Am. Brands, Inc.,                              |

| 450 U.S. 79 (1981)                                       |

| 100 0.0. 77 (1701)                                       |

| Cf. Am. Target Advert., Inc. v. Giani,                   |

| 199 F.3d 1241 (10th Cir. 2000)6, 48                      |

| Cf. Andrew v. Am. Import Ctr.,                           |

| 110 A.3d 626 (D.C. 2015)5                                |

| 110 11.3d 020 (D.C. 2013)                                |

| Cf. Elrod v. Burns,<br>427 U.S. 347 (1976)                                                                                                                                                | 8      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Cohen v. Beneficial Indus. Loan Corp.,<br>337 U.S. 541 (1949)                                                                                                                             | 9      |

| Diouf v. Mukasey,<br>542 F.3d 1222 (9th Cir. 2008)                                                                                                                                        | 33     |

| Donlon Indus., Inc. v. Forte,<br>402 F.2d 935 (2d Cir. 1968)                                                                                                                              | 9      |

| Farmer v. Alpha Techs., Inc.,<br>No. 1:14-CV-2958, 2015 WL 13777260 (N.D. Ga. Nov. 18, 2015), report of<br>recommendation adopted, No. 1:14-CV-2958, 2015 WL 13777898 (N.D. Dec. 9, 2015) | . Ga.  |

| Felder v. Casey,<br>487 U.S. 131 (1988)                                                                                                                                                   | 44, 48 |

| Free v. Bland,<br>369 U.S. 663 (1962)                                                                                                                                                     | 43     |

| Gen. Elec. Co. v. Joiner,<br>522 U.S. 136 (1997)                                                                                                                                          | 33     |

| Gen–Probe, Inc. v. Amoco Corp.,<br>926 F. Supp. 948 (S.D. Cal. 1996)                                                                                                                      | 44     |

| Globetrotter Software, Inc. v. Elan Comput. Grp., Inc.,<br>362 F.3d 1367 (Fed. Cir. 2004)                                                                                                 | 14, 47 |

| Golan v. Pingel Enter., Inc.,<br>310 F.3d 1360 (Fed. Cir. 2002)                                                                                                                           | 37     |

| Gulfstream Aerospace Corp. v. Mayacamas Corp.,<br>485 U.S. 271 (1988)                                                                                                                     | 5      |

| Halo Elecs., Inc. v. Pulse Elecs., Inc.,<br>579 U.S. 93 (2016)                                                                                                                            |        |

| 380 U.S. 460 (1965)                                                                                            | 51         |

|----------------------------------------------------------------------------------------------------------------|------------|

| Hines v. Davidowitz,<br>312 U.S. 52 (1941)                                                                     | 43         |

| Ice Castles v. LaBelle Lake Ice Palace, LLC,<br>No. 4:18-cv-00571, 2021 WL 3085479 (D. Idaho July 21, 2021)    | 46         |

| <i>In re Apple Inc.</i> ,<br>979 F.3d 1332 (Fed. Cir. 2020)                                                    | 13, 53     |

| In re Deutsche Bank Tr. Co. Americas,<br>605 F.3d 1373 (Fed. Cir. 2010)                                        | 15         |

| <i>In re Princo Corp.</i> ,<br>478 F.3d 1345 (Fed. Cir. 2007)                                                  | 12, 14     |

| In re Shared Memory Graphics LLC,<br>659 F.3d 1336 (Fed. Cir. 2011)                                            | 13, 14, 33 |

| <i>In re U.S. for Use &amp; Benefit of St. Paul A. M. E. Church Hous. Corp.</i> , 541 F.2d 463 (4th Cir. 1976) | g          |

| Klocke v. Watson,<br>936 F.3d 240 (5th Cir. 2019)                                                              | 45, 52     |

| Landmark Tech., LLC v. Azure Farms, Inc.,<br>No. 3:18-CV-1568, 2020 WL 1430088 (D. Or. Mar. 24, 2020)          | 34         |

| LEGO A/S v. ZURU Inc.,<br>799 F. App'x 823 (Fed. Cir. 2020)                                                    | 32         |

| Lone Star Silicon Innovations LLC v. Nanya Tech. Corp.,<br>925 F.3d 1225 (Fed. Cir. 2019)                      | 28         |

| Matter of Establishment Inspection of Skil Corp.,<br>846 F.2d 1127 (7th Cir. 1988)                             | 4          |

| <i>Melaleuca, Inc. v. Hansen,</i><br>No. CV07-212-E-EJL, 2008 WL 2788470 (D. Idaho July 18, 2008)4           | 18         |

|--------------------------------------------------------------------------------------------------------------|------------|

| <i>Mitchell v. Forsyth</i> ,<br>472 U.S. 511 (1985)1                                                         | 0          |

| NAPCO, Inc. v. Landmark Tech. A, LLC,<br>555 F. Supp. 3d 189 (M.D.N.C. 2021)3                                | 38         |

| Negrete v. Allianz Life Ins. Co. of N. Am., 523 F.3d 1091 (9th Cir. 2008)                                    | 33         |

| <i>Procter &amp; Gamble Co. v. Kraft Foods Glob., Inc.,</i> 549 F.3d 842 (Fed. Cir. 2008)1                   | 12         |

| Puritan Med. Prods. Co. v. Copan Italia S.p.A.,         188 A.3d 853 (Me. 2018)                              | 34         |

| Shady Grove Orthopedic Assocs., P.A. v. Allstate Ins. Co., 559 U.S. 393 (2010)                               | 52         |

| SSI Techs., LLC v. Dongguan Zhengyang Elec. Mech. LTD., 59 F.4th 1328 (Fed. Cir. 2023)5                      | 50         |

| Sumitomo Copper Litig. v. Credit Lyonnais Rouse, Ltd.,<br>262 F.3d 134 (2nd Cir. 2001)1                      | 15         |

| <i>Thermolife Int'l LLC v. GNC Corp.</i> , 922 F.3d 1347 (Fed. Cir. 2019)4                                   | <b>‡</b> 1 |

| Triple7Vaping.com, LLC v. Shipping & Transit LLC, No. 16-CV-80855, 2017 WL 5239874 (S.D. Fla. Feb. 6, 2017)3 | 38         |

| <i>United States v. Hampshire</i> ,<br>95 F.3d 999 (10th Cir. 1996)3                                         | 32         |

| Virtue v. Creamery Package Mfg. Co.,<br>227 U.S. 8 (1913)31, 41, 44, 4                                       | <b>1</b> 7 |

| Zafer Constr. Co. v. United States,     |    |

|-----------------------------------------|----|

| 40 F.4th 1365 (Fed. Cir. 2022)          | 32 |

| ,                                       |    |

| S4-4-4                                  |    |

| Statutes                                | 2  |

| 28 U.S.C. § 1292                        |    |

| 28 U.S.C. § 1295(a)(1)                  |    |

| 28 U.S.C. § 1338                        |    |

| 28 U.S.C. § 1651                        |    |

| 35 U.S.C. § 100(d)                      |    |

| 35 U.S.C. § 281                         |    |

| 35 U.S.C. § 284                         |    |

| 35 U.S.C. § 285                         |    |

| 48-1706(1)(b)-(d)                       |    |

| 6 R.I. Gen. Laws Ann. § 6-41.1-5 (West) |    |

| Act § 48-1701(1)(b)                     |    |

| Act § 48-1701(2)                        |    |

| Act §48-1702(3)(b)                      |    |

| Act § 48-1703(1)                        |    |

| Act § 48-1703(2)(b)                     |    |

| Act § 48-1703(3)                        |    |

| Act § 48-1703(3)(b)                     |    |

| Act § 48-1703(3) (c)(ii)                |    |

| Act § 48-1706(1)(d)                     |    |

| Act § 48-1707                           |    |

| Fed. R. Civ. P. 11                      |    |

| Fed. R. Civ. P. 23(f)                   |    |

| Ga. Code Ann. § 10-1-772 (West)         |    |

| Idaho Code §§ 48-1707                   |    |

| Ind. Code Ann. § 24-11-2-5 (West)       |    |

| Ind. Code Ann. § 24-11-4-1 (West)       |    |

| Me. Rev. Stat. tit. 14, § 8701          |    |

| Mich. Comp. Laws § 446.169              |    |

| Miss. Code Ann. § 75-24-355, -357       |    |

| Mont. Code Ann. § 30-13-154             |    |

| N.C. Gen. Stat. Ann. § 75-142           |    |

| N.C. Gen. Stat. Ann. § 75-144           |    |

| N.D. Cent. Code Ann. § 51-36-05 (West)  |    |

| N.H. Rev. Stat. Ann. § 359-M:3          |    |

| S.D. Codified Laws § 37-36-5            | 20 |

| Tenn. Code Ann. § 29-10-103, -104        | 20 |

|------------------------------------------|----|

| Utah Code Ann. § 78B-6-1905 (West)       |    |

| Vt. Stat. Ann. tit. 9, § 4198            |    |

| Wash, Rev. Code Ann. § 19.350.010 (West) |    |

### TABLE OF ABBREVIATIONS AND CONVENTIONS

Katana Patent owner and Appellant Katana Silicon Technologies

LLC in Case No. 23-2095

Longhorn Appellant Longhorn IP LLC in Case No. 23-2007

'879 Patent Asserted U.S. Patent No. 6,352,879 owned by Katana,

Appx56-79

'013 Patent Asserted U.S. Patent No. 6,731,013 owned by Katana,

Appx80–114

'806 Patent Asserted U.S. Patent No. RE38,806 owned by Katana,

Appx31–55

Asserted Patents The '879 Patent, '013 Patent, and '806 Patent

Micron Appellees Micron Technology, Inc., Micron Semiconductor

Products, Inc., and Micron Technology Texas, LLC

Order Memorandum Decision and Order filed May 3, 2023,

Appx1-30

BFA Bad-faith assertion of patent infringement

Act Title 48, Chapter 17 of the Idaho Code, entitled "Bad Faith

Assertions of Patent Infringement"

BFA bond A bond under a state's BFA statute

In quotations, all emphasis is added unless otherwise noted.

## I. INTRODUCTION

In the underlying cases, the district court applied a state statute to order an \$8 million bond as a precondition to Katana prosecuting its patent case against Micron. The Order addresses a bond motion Micron originally filed in a retaliatory lawsuit in Idaho state court against a Katana affiliate, Longhorn. The Order expressly precludes Katana from prosecuting its federal infringement case unless and until the \$8 million bond is paid. The district court embraced Micron's presumed intent in seeking the bond that Katana would be "scared off" from enforcing its patent rights. Appx1175–1181 (Order Denying Motion to Stay Bond Proceeding) at Appx178. What evidence did the district court consider in determining that Idaho law should effectively preclude Katana from proceeding with its federal case? None. Instead, the district court in Boise decided that the Idaho Act required the massive bond based on mere allegations of a BFA leveled by home-town juggernaut Micron.

The Order imposes what appears to be the first BFA bond in American history, and it further appears to present this Court's first opportunity to consider the constitutionality of any state's BFA statute. Such statutes are now common, but the Idaho Act is an outlier in important ways. Indeed, with its uncapped bond provision and express targeting of federal complaints, the Act is arguably the most extreme BFA statute in the country. Appellants submit the Act and particularly its bond provision are unconstitutional and preempted, especially as applied in the Order.

Notably, this case is more egregious than prior preemption cases this Court has considered. There is no underlying antitrust violation or customer interference or other traditional tort here. And not only is there no clear and convincing evidence of bad faith as this Court's precedents would require, the Order cites no evidence at all—just (demonstrably untrustworthy) *allegations* of the disgruntled accused infringer. Yet on the basis of these allegations alone, the Order effectively punishes Katana under state law for petitioning a federal court for a federal remedy.

Given the magnitude of the bond, Micron's economic leverage over the much smaller patent owner, and the procedural posture of these cases, awaiting an appeal following a final judgment in the underlying cases against Katana and/or Longhorn is neither realistic nor just. Appellants submit, therefore, that immediate relief from this Court is both necessary and appropriate.

## II. STATEMENT OF RELATED CASES

No other appeals in or from these actions has previously been before this or any other appellate court.

## III. JURISDICTIONAL STATEMENT

This appeal is timely. The Order was filed on May 3, 2023, and each of Katana and Longhorn filed its respective notice of appeal on May 25, 2023.

## A. Interlocutory Appeal

The Order imposes an unconstitutional bond calculated under Idaho state law by quadrupling estimated fees and costs Micron may incur in Katana's patent case. The chilling effect of the \$8 million bond is manifest. And it was ordered below based not on evidence, but on Micron pleadings alone, assumed (wrongly) to be true. Appx28 (applying "a reasonable possibility" standard lower than "the higher 12(b)(6) standard"). Thus, Idaho's scheme would allow patent infringers in Idaho to erect an often insurmountable barrier to federal court for smaller patent owners falsely accused of bad faith. The Order in this case erected just such a barrier. This appeal is therefore ripe at least under 28 U.S.C. § 1292 and the *Cohen* (collateral order) doctrine.

1. This Court Has Jurisdiction Under Section 1292(a)(1) & (c)(1).

Katana has been effectively enjoined from enforcing its federal rights in federal court because of a state statute asserted in a bond motion—filed only in Micron's separate case against Longhorn, a separate company. The Supreme Court

3

assumption based on Micron's pleadings alone. See Appx3-4 & Appx21 (referring to "Longhorn, which allegedly controls Katana"; concluding Katana's infringement

<sup>&</sup>lt;sup>1</sup> The jurisdictional analysis as to Katana applies equally to Longhorn on the current record. Micron has argued that activities of Longhorn, a Katana affiliate and service provider, are attributable to Katana and that Katana's filing of a federal complaint is attributable to Longhorn. See Appx384–408 (Micron Memo. ISO Motion for Bond) at Appx401. Micron also says its BFA claim against Katana was a compulsory counterclaim in Katana's patent infringement suit. Appx150–175 (Micron v. Longhorn Complaint) at Appx154 n.2. The Order adopts Micron's argument as an

recently reiterated that "where an order has the 'practical effect' of granting or denying an injunction, it should be treated as such for purposes of appellate jurisdiction." *Abbott v. Perez*, 138 S. Ct. 2305, 2310 (2018); *see also Matter of Establishment Inspection of Skil Corp.*, 846 F.2d 1127, 1130 (7th Cir. 1988) (holding that an order requiring a manufacturer to allow a government agency to inspect records or else pay \$500 per day was literally an injunction for appealability purposes). In *Abbott v. Perez*, the Supreme Court stressed the "valuable purpose" of the "practical effect' rule": "But if the availability of interlocutory review depended on the district court's use of the term 'injunction' or some other particular language, Congress's scheme could be frustrated." 138 S. Ct. at 2319–20.

If an interlocutory order is not an injunction but has the "practical effect" of one, appellate jurisdiction nevertheless exists under Section 1292 where the order "might have 'serious, perhaps irreparable, consequence" and can be "effectually challenged' only by immediate appeal." *Carson v. Am. Brands, Inc.*, 450 U.S. 79, 84 (1981); *see also Gulfstream Aerospace Corp. v. Mayacamas Corp.*, 485 U.S. 271,

complaint in 2022 was a new assertion by Longhorn for purposes of the Act's limitations period). While Micron's position lacks merit (see Appx1182–1207 (Longhorn Response to Micron's Motion for Bond) at Appx1200–1202), the Order's assumption of that position means Longhorn and Katana are similarly situated for purposes of appellate jurisdiction. Moreover, because Katana and Longhorn, and the injunction and bond, are addressed "concurrently in a single order," they are in that sense "inextricably linked." See Murata Mach. USA v. Daifuku Co., 830 F.3d 1357, 1361 (Fed. Cir. 2016).

287–88 (1988) ("Section 1292(a)(1) will, of course, continue to provide appellate jurisdiction over orders that grant or deny injunctions and orders that have the practical effect of granting or denying injunctions and have serious, perhaps irreparable, consequence." (cleaned up)).

## a. The Order Is Injunctive.

The injunctive nature of the Order is not ambiguous: "Longhorn or Katana must post a bond of \$8 million before the Katana case (1:22-cv-00282) may proceed further." Appx30. This anti-enforcement injunction was imposed on Katana based on a motion for bond filed in state court only against *Longhorn*, and it is not merely a stay or case management order as Micron has argued. The injunction has no stated end date and presents an unacceptable risk of irreparable harm to Katana, the patent owner. Cf. Andrew v. Am. Import Ctr., 110 A.3d 626, 634 (D.C. 2015) ("[G]ranting a stay pending arbitration does have the 'practical effect' of enjoining the party opposing arbitration.") (as cited in *Abbott*, 138 S. Ct. at 2321 n.12). The district court itself, in ordering that Longhorn had to respond to Micron's bond motion without any discovery, recognized the presumptive intent of Micron seeking a bond of such coercive magnitude is that Katana "would be scared off" from enforcing its federal patent rights. Appx1178.

b. The Injunction and Bond Are Punitive and Chilling in Their Effect, Requiring Immediate Appeal.

Courts consistently recognize the chilling ("scared off") impact that even much lower bonds have on speech and on enforcement of rights—an impact often giving rise to constitutionality concerns, as it does here. See, e.g., Am. Target Advert., Inc. v. Giani, 199 F.3d 1241, 1250 (10th Cir. 2000) ("The chilling impact of the bond upon protected speech outweighs any fraud protection it might provide. We therefore find that the bond/letter of credit provision of the Utah Act is unconstitutional on its face."); Buchanan v. Sullivan, No. 8:20-CV-301, 2021 WL 149052, at \*4 (D. Neb. Jan. 15, 2021) ("The Court also finds that more than a minimal bond might chill private enforcement of the TCPA, counter to congressional intent."). And the larger and more indeterminate or speculative the bond, the greater the risk of chilling meritorious litigation. See Azizian v. Federated Dep't Stores, Inc., 499 F.3d 950, 960 (9th Cir. 2007) ("[A] Rule 7 bond including the potentially large and indeterminate amounts awardable under Rule 38 [providing for an award of attorneys' fees as a sanction] is more likely to chill an appeal than a bond covering the other smaller, and more predictable, costs on appeal.").

A state could scarcely concoct a larger, more indeterminate bond formula than Idaho's. Its Act stands alone among the many BFA statutes in the country by purporting expressly to make "unlawful" the inclusion of certain assertions in a

federal "complaint." Act § 48-1703(1).<sup>2</sup> And it is one of less than a handful of state BFA statutes that provide for a bond to include quadruple the anticipated damages, costs, and attorney's fees, with no cap on the bond amount. Act §§ 48-1707 & 48-1706(1)(b)-(d). See infra notes 6-7 and accompanying text.

Here, the bond itself is coercive and punitive—punishing Katana for filing its federal complaint—such that meaningful appellate review must be interlocutory. Micron itself has emphasized that "its [BFA] claims are centered on the Katana Complaint" (Appx1131–1157 (Opp. to Longhorn's Motion to Dismiss) at Appx1139), and in its lawsuit against Longhorn, Micron focused on the filing of that *Katana* complaint (Appx153 & n.1). Moreover, addressing *Erie* considerations, the district court reasoned that "the bond is not merely procedural—it is a substantive provision that discourages bad-faith patent assertion *in and of itself*." Appx27. The district court further confirmed the punitive, coercive purpose of the bond when it rejected Longhorn's request for limited discovery to respond to the bond motion on the grounds that any delay in ordering a bond "would be undercutting" the Act "in a

2

<sup>&</sup>lt;sup>2</sup> A minority of the states with BFA statutes define "target" broadly enough to include persons who have been sued, but they do not appear expressly to regulate the contents of a (federal court) "complaint" as Idaho does. *See, e.g.*, N.C. Gen. Stat. § 75-142; Wash. Rev. Code § 19.350.010; Ind. Code § 24-11-2-5.

<sup>&</sup>lt;sup>3</sup> What the district court missed is that the bond provision also discourages *good-faith* patent assertions in a federal complaint, in part because the court applied the provision based merely on the accused infringer's allegations, without considering any of the evidence contradicting those allegations.

manner that removes *much of the teeth* from the law." Appx1180. Thus, the bond is being used substantively as a state-law device with "teeth" to discourage enforcement of federal rights, not simply as a procedural tool to provide security for a possible damages award under the Act.

Micron no doubt counts on Katana to fold up its tent and go home rather than face the prospect of years of litigation in Micron's Idaho hometown on Micron's state-law BFA claim seeking quadruple damages, while Katana's affirmative federal-law claim seeking compensation for patent infringement is barred from proceeding absent an \$8 million bond. This motivation is particularly apparent given the economic and size disparity between (a) accused infringer Micron—the selfdescribed "Fortune 500 leader" that "spends billions of dollars each year" (No. 2023-2007, ECF No. 16 at 2)—and (b) patent owner Katana—the small company that Micron implies will "bend or break when struck" (id. at 4 n.3). Micron's tooapparent strategy is to leverage its economic power and the bond to force Katana to give up its federal rights. The constitutional implications of this risk buttress the irreparable nature of Katana's injury. Cf. Elrod v. Burns, 427 U.S. 347, 373-74 (1976) (affirming a preliminary injunction, holding that the "loss of First Amendment freedoms, for even minimal periods of time, unquestionably constitutes irreparable injury"); Fed. R. Civ. P. 23(f) advisory committee note to 1998 amendment (recognizing that an order granting class certification could "force a

defendant to settle rather than incur the costs of defending a class action and run the risk of potentially ruinous liability"). Even if the Order were not considered a literal injunction, interlocutory relief would still be required given this grave risk of irreparable harm and the chilling effect of the Order.

2. This Court Also Has Jurisdiction Under the Collateral Order Doctrine Applied to Bonds, as in Cohen.

Aside from Section 1292 appellate jurisdiction, this appeal is also timely under the collateral-order doctrine set forth in Cohen v. Beneficial Indus. Loan Corp., 337 U.S. 541 (1949). Cohen itself involved a litigation bond as a precondition to bringing a suit. At issue here is the Idaho district court's power to order a bond at all, which is a classic issue for interlocutory appeal, especially given the magnitude of the bond. See Donlon Indus., Inc. v. Forte, 402 F.2d 935, 936 (2d Cir. 1968) (reciting "familiar law" that interlocutory orders granting applications for security are appealable "when the appeal challenges the court's power"); see also In re U.S. for Use & Benefit of St. Paul A. M. E. Church Hous. Corp., 541 F.2d 463, 464 (4th Cir. 1976) ("An order requiring or refusing to require the posting of security during the pendency of the litigation is 'collateral' and is appealable under the doctrine of Cohen."). And as in Cohen, the "order of the District Court did not make any step toward final disposition of the merits of the case and will not be merged in final judgment. When that time comes, it will be too late effectively to review the present order." 337 U.S. at 546. Micron has argued the Order is not "completely separate

from the merits" as *Cohen* requires because the bond requirement considers the ultimate merits question of bad faith. No. 2023-2007, ECF No. 16 at 15. But the Order was based purely on Micron's *allegations*, and the Supreme Court has rejected reasoning like Micron's in that circumstance. *See Mitchell v. Forsyth*, 472 U.S. 511, 528–29 (1985) ("[T]he Court has recognized that a question of immunity is separate from the merits of the underlying action for purposes of the *Cohen* test *even though a reviewing court must consider the plaintiff's factual allegations* in resolving the immunity issue."). Moreover, the Order here takes no more "step toward final disposition of the merits" than did the order in *Cohen*.

"Here it is the right to security [(a bond)] that presents a serious and unsettled question," as opposed to merely "an exercise of discretion as to the amount of security." *Cohen*, 337 U.S. at 547.<sup>4</sup> This Court is being asked to decide as a matter of first impression whether prosecuting a federal patent-infringement claim can be

\_

<sup>&</sup>lt;sup>4</sup> Some courts hold that bond orders (accompanying preliminary injunctions, for example) are not subject to interlocutory appeal where they involve merely "an exercise of discretion as to the amount of security." *Donlon*, 402 F.2d at 936 (Friendly, C.J.). *Donlon* reasoned that a court's "power" to require a bond, in contrast with matters of discretion about the exact amount of the bond, "is an issue of law, and an appellate decision will settle the matter not simply for the case in hand but for many others—as was notably true with the important issue in *Cohen*." *Id.* at 937. But even where the issue is only one of discretion concerning merely the amount of the bond, interlocutory appeals are permissible when "the bond is both higher than necessary and beyond the plaintiff's financial capacity, and thus inflicts irreparable harm without justification. In such a case the bond order meets the criteria for a collateral order." *Habitat Educ. Ctr. v. U.S. Forest Serv.*, 607 F.3d 453, 456 (7th Cir. 2010) (citations omitted).

conditioned on first posting a massive state-law bond, particularly when the need for the bond is based on nothing more than allegations. The punitive aspect of the bond requirement will have already done its irreparable damage if Appellants had to survive, without being forced into an adverse settlement or bankruptcy, and wait for a final judgment on the merits before they could one day appeal the bond. These circumstances are precisely the sort that *Cohen*'s collateral-order doctrine is designed to address.

Micron has argued that Katana can wait to get a final judgment on the BFA claim and then "appeal at that point" (No. 2023-2007, ECF No. 16 at 13), but this ignores the import of a punitive, coercive bond. Micron's argument that "the bond is not conclusive" likewise rings hollow. *Id.* at 14. The bond conclusively erects a massive barrier to enforcing federal rights. The harm from that barrier is precisely what gives rise to the interlocutory appeal. Perhaps \$8 million is a small amount for Micron, but it would likely close the courthouse doors on the majority of patent owners in the United States damaged by Idaho companies' infringement.

For this reason, and because the appeal questions the district court's power to order the bond, the same reasoning and holding of *Cohen* should apply to allow interlocutory appeal of the Order in this case.

## 3. The Court May Also Exercise Pendent Jurisdiction.

Finally, at the Court's discretion, related issues may also be included in the appeal based on pendent jurisdiction. *Procter & Gamble Co. v. Kraft Foods Glob., Inc.*, 549 F.3d 842, 846 (Fed. Cir. 2008) ("When this court reviews a properly appealable interlocutory order, 'other interlocutory orders, which ordinarily would be nonappealable standing alone, may be reviewed.""). Where the lower court decides additional issues along with an appealable issue in a single interlocutory order, the appellate court may conclude "those decisions are inextricably linked" and exercise its discretion to consider the additional issues. *Murata*, 830 F.3d at 1361. Thus, Appellants also seek relief from the Order's denial of their motions to dismiss.

## B. Alternative Relief Under 28 U.S.C. § 1651

Alternatively, this Court has mandamus jurisdiction under the All Writs Act, 28 U.S.C. § 1651, and because (a) the underlying Katana case is a patent case, (b) the underlying Longhorn case also arises under federal patent law, and (c) the district court precluded Katana's patent case based on Micron's motion filed only in the Longhorn case and addressed Katana and Longhorn concurrently in a single order. 28 U.S.C. § 1295(a)(1); *In re Princo Corp.*, 478 F.3d 1345, 1351–52 (Fed. Cir. 2007) (confirming this Court's exclusive jurisdiction over writs of mandamus where jurisdiction in the district court is based in whole or in part on 28 U.S.C. § 1338, even where the writ substantively does not implicate patent law).

Mandamus is "available to correct a clear abuse of discretion." *In re Apple Inc.*, 979 F.3d 1332, 1336 (Fed. Cir. 2020). In general, three conditions must be satisfied for a writ to issue: "(1) the petitioner must demonstrate a clear and indisputable right to issuance of the writ; (2) the petitioner must have no other adequate method of attaining the desired relief; and (3) the court must be satisfied that the writ is appropriate under the circumstances." *Id.* (citing *Cheney v. United States Dist. Ct.*, 542 U.S. 367, 380–81 (2004)). Given "the unique relationship of this issue to patent law," Federal Circuit law governs. *In re Deutsche Bank Tr. Co. Americas*, 605 F.3d 1373, 1378 (Fed. Cir. 2010) (concluding Federal Circuit law governed "the determination of whether a protective order should include a patent prosecution bar"). Each condition for mandamus is met here.

It is "clear and undisputable" that the district court's order was unconstitutional and otherwise erroneous as a matter of law. And an error on a question of law or application of the law to the facts qualifies as an abuse of discretion. *In re Shared Memory Graphics LLC*, 659 F.3d 1336, 1342 (Fed. Cir. 2011) ("SMG") (granting mandamus where the district court misconstrued a joint defense agreement and thereby erroneously granted a motion to disqualify trial counsel). The Order leveraged the state Act to punish patent owner Katana for asserting its federal patent rights in federal court and to erect a substantial barrier to Katana's ability to prosecute its infringement case. And it did so with no evidence

of bad faith at all, much less the clear and convincing evidence of objective and subjective bad faith required to overcome the bar on state-law liability for communications or petitioning activity related to patent infringement. *Globetrotter Software, Inc. v. Elan Comput. Grp., Inc.*, 362 F.3d 1367, 1374–75 (Fed. Cir. 2004). Thus, the district court's error is clear from both the bond provision itself and federal preemption jurisprudence.

Appellants lack "adequate alternative means to obtain the relief sought." In re *Princo*, 478 F.3d at 1353. Katana and Longhorn have been ordered to post not some de minimis bond, but a bond quadruple Micron's estimated patent-litigation-defense fees and costs—a bond understood by the district court to serve a "similar purpose to the damages provisions" and to provide "much of the teeth" of the Act to further "prompt resolution" of the patent infringement claims because Katana would be "scared off" from the case. Appx1178–1180. In other words, the idea is to force Katana to abandon its patent infringement claims. In these circumstances, waiting to appeal a final judgment is inadequate. See SMG, 659 F.3d at 1340-42 (granting mandamus, when appeal was unavailable under the collateral-order doctrine, where the district court erred as a matter of law in disqualifying patent owner SMG's counsel-of-choice, and reasoning that the patent owner would be "adversely affected if it is required to wait until after a final adverse judgment to have this issue addressed"); cf. Sumitomo Copper Litig. v. Credit Lyonnais Rouse, Ltd., 262 F.3d

134, 140 (2nd Cir. 2001) (acknowledging that "class certification will effectively terminate the litigation because it will force [defendants] to settle the case rather than risk trial").

Finally, the requested writ is "appropriate under the circumstances." *In re Apple Inc.*, 979 F.3d at 1336. This case would not be the first time that mandamus was warranted concerning an issue of first impression. *See In re Deutsche Bank*, 605 F.3d at 1377, 1382 (noting that "we have granted mandamus review of discovery orders when the petition presented an important issue of first impression," and granting the mandamus petition where the district court improperly evaluated a proposed prosecution bar for a protective order).

## IV. STATEMENT OF THE ISSUES

Whether the district court erred by declining to dismiss Micron's BFA claims against Katana and Longhorn and by ordering that Katana's patent infringement claims against Micron cannot proceed until Katana or Longhorn posts an \$8 million bond where (i) the Idaho Act and its bond provision on their face and as applied are preempted by federal law, and (ii) Micron's factual allegations failed to state a plausible claim of the minimum objective bad faith required by this Court's preemption decisions.

Whether the district court clearly abused its discretion in granting Micron's motion filed against Longhorn for a multi-million-dollar bond under state law